### Universidad Miguel Hernández de Elche

Departamento de Ciencia de Materiales, Óptica y Tecnología Electrónica

# Design and implementation of FPGA-based video encoding accelerators

PhD Thesis

A dissertation for the degree of Doctor in Industrial and Telecommunication Technologies by: Estefanía Fátima Alcocer Espinosa Advisors: Otoniel Mario López Granado Roberto Gutiérrez Mazón

### Universidad Miguel Hernández de Elche

Departamento de Ciencia de Materiales, Óptica y Tecnología Electrónica

# Design and implementation of FPGA-based video encoding accelerators

Tesis Doctoral

Memoria presentada para optar al grado de Doctora en Tecnologías Industriales y de Telecomunicación por: Estefanía Fátima Alcocer Espinosa

> *Dirigida por:* Otoniel Mario López Granado Roberto Gutiérrez Mazón

D. OTONIEL MARIO LÓPEZ GRANADO, Profesor Contratado Doctor de la Universidad Miguel Hernández de Elche y D. ROBERTO GUTIÉRREZ MAZÓN, Profesor Contratado Doctor de la Universidad Miguel Hernández de Elche,

#### CERTIFICAN:

Que la presente memoria *Design and implementation of FPGA-based video encoding accelerators*, ha sido realizada bajo su dirección, en el Departamento de Ciencia de Materiales, Óptica y Tecnología Electrónica de la Universidad Miguel Hernández de Elche, por la Ingeniera Dña. Estefanía Fátima Alcocer Espinosa, y constituye su tesis para optar al grado de Doctora.

Para que conste, en cumplimiento de la legislación vigente, autorizan la presentación de la referida tesis doctoral ante la Comisión de Doctorado de la Universidad Miguel Hernández de Elche, firmando el presente certificado.

Fdo. D. Otoniel M. López Granado

Fdo. D. Roberto Gutiérrez Mazón

D. PIEDAD NIEVES DE AZA MOYA, Catedrática de Universidad y directora del Departamento de Ciencia de Materiales, Óptica y Tecnología Electrónica de la Universidad Miguel Hernández de Elche,

#### CERTIFICA:

Que la presente memoria *Design and implementation of FPGA-based video encoding accelerators*, realizada bajo la dirección de D. OTONIEL MARIO LÓPEZ GRANADO y D. ROBERTO GUTIÉRREZ MAZÓN, en el Departamento de Ciencia de Materiales, Óptica y Tecnología Electrónica de la Universidad Miguel Hernández de Elche, por la Ingeniera Dña. Estefanía Fátima Alcocer Espinosa, constituye su tesis para optar al grado de Doctora.

Para que conste, en cumplimiento de la legislación vigente, autoriza la presentación de la referida tesis doctoral ante la Comisión de Doctorado de la Universidad Miguel Hernández de Elche, firmando el presente certificado.

Fdo. D. Piedad Nieves De Aza Moya

### Acknowledgements

"Los dioses se han marchado, nos queda la televisión". Manuel Vázquez Montalbán

A mis personas favoritas en el mundo.

Gracias a mi familia. A mis padres, hermana y abuelos por ser los impulsores de todos mis sueños, donantes de inspiración. A Andrés por ser mi mitad y estar incondicionalmente a mi lado cuando más lo he necesitado. Sois mis personas favoritas en el mundo. Esto es por y para vosotros.

Gracias a mis directores de tesis. A Otoniel y Roberto porque nunca me han dejado sola durante este proceso, porque me han animado, ayudado y aguantado, y sobre todo, porque han demostrado ser mis amigos. También sois mis preferidos, no os cambiaría nunca.

Gracias a mis compañeros de GATCom. Al boss Mels, Pablo, Miguel, Héctor, Vicente y Oto again, por tratarme desde el primer día como una más, por las comilonas, partidas y risas que hemos compartido, porque os habéis convertido en unos amigos auténticos. Porque sois como de mi familia, concretamente como mis tíos, y a la familia hay que quererla.

Gracias a los compañeros de la Universidad de Gent que me acogieron con los brazos abiertos. A Jan, Glenn, Ruben, Niels, Tom y Johan por ser tan amables durante mi estancia.

Gracias a todos los que han escuchado la palabra tesis salir de mi boca, aunque fuera por un segundo. A mis tíos, amigas y medio Bigastro.

Mil gracias.

### Abstract

Nowadays, having the latest image and video gadgets is trendy. Commercially, high performance multimedia devices are offered and/or demanded increasingly, such as very high-resolution TVs with high quality of image (Ultra High Definition (UHD)), video cameras that capture at very high frame rates, etc. Every day, millions of "selfies", "gifs", "boomerangs" are immediately uploaded to social networks such as Instagram, Facebook or Twitter, and even we broadcast live our experiences with applications such as PeriScope. We are also spectators in first person of the most extreme sports which are recorded with Go-Pro cameras or similar. This is the reason why, in the field of image and video, many innovations and improvements will continue to be brought about due to the trend of high consumption on commercial multimedia devices.

Although nowadays we can find devices capable of reproducing and capturing very high resolution videos at high frame rates, this involves higher complexity in video data processing. Videos with previous requirements contain such a high amount of data that entails some problems such as the difficulty for video transmition in real time, the need for a large bandwidth that is almost unacceptable, the limited memory storage, and high power consumption, among others.

In order to overcome the above limitations, different coding standards have been developed over the years, trying to adapt to the market needs on each moment. As overview, video encoders compress the information so that it can be stored or transmitted occupying as little space as possible. As an example, platforms like Netflix use Google's VP9 compression codec to allow users download movies and series not needing too much storage space in order to watch them offline on any device. In order to achieve this compression, it is taken advantage of the huge redundancy of video sequences in both spatial and temporal domains. Thus, by removing such redundant information, it is possible to optimally encode video contents.

Therefore, due to the resource requirements, and the consequent increase in the complexity, and the processing time, this dissertation investigates the use of hardware accelerators based on Field Programmable Gate Array (FPGA)s on the most complex parts that require more processing time in the video encoders.

Firstly, a hardware accelerator has been designed for the computation of the Motion Estimation (ME) of a High Efficiency Video Coding (HEVC) video encoder. In this case, the work has been focused on the latest video coding standard HEVC, which achieves the best compression efficiency in relation with its predecessors. As in previous standards, the removal of temporal redundancy demands an overwhelming computational cost, especially in high resolution video sequences. Therefore, the ME block (Inter prediction) of an encoder is one of the most critical modules in video compression. Based on this context, our design is based on the implementation of the ME block of a HEVC encoder on a FPGA, proposing two new and innovative techniques in both the tree adder for Sum of Absolute Differences (SAD) computation and the memory reading order. The results show that using our hardware ME module, a HEVC encoder is capable of encoding very high resolution video sequences faster than in real time.

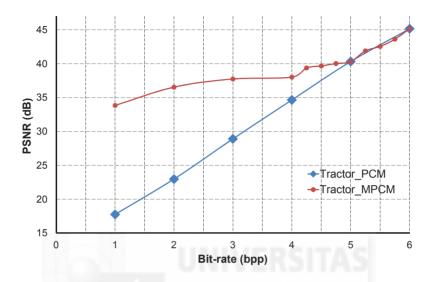

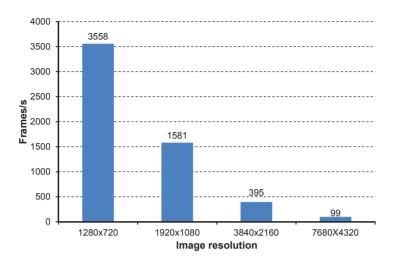

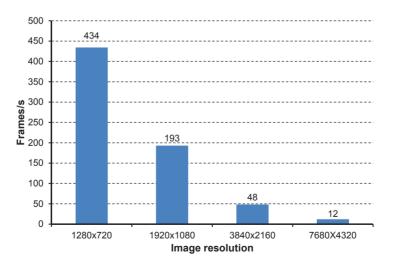

Secondly, we present a FPGA-based hardware implementation of a very simple codec called Module Pulse Code Modulation (MPCM) based on the elimination of spatial redundancy (Intra prediction). This codec has the same advantages as Pulse Code Modulation (PCM) coding, reducing considerably the required bandwidth and maintaining the same image quality. The experimental results obtained demonstrate that our hardware implementation allows the continuous recording of a nowadays high-speed camera at a good quality image resolution.

This dissertation has been done under the modality of presentation of doctoral thesis with a set of publications, included in the regulations of the Miguel Hernández University of Elche. In compliance with these regulations, the publications that compose this dissertation have been included as an annex, and the sections corresponding to the research general description, the overall summary of the results obtained, and the final conclusions have been developed.

## Resumen

Hoy en día poseer el último grito en dispositivos de vídeo e imagen no es nada sorprendente, de hecho, es la tendencia actual. Comercialmente, los dispositivos de altas prestaciones como televisores de muy alta resolución con una gran calidad de imagen o videocamáras que capturan a muy altas tasas de frames se ofertan y demandan cada vez más. Todos los días, se realizan millones de "selfies", "gifs", "boomerangs" que son inmediatamente subidos a redes sociales como Instagram, Facebook o Twitter; incluso transmitimos nuestra vida en directo con aplicaciones como PeriScope. También somo espectadores en primera persona de los deportes más extremos que son grabados en directo con cámaras del tipo Go-Pro. Es por ello, que el ámbito de la imagen y vídeo es un campo con futuro, en el cual cada día se aportan innumerables innovaciones y mejoras debido al consumo actual de dichos dispositivos comerciales.

Aunque cada vez es más fácil encontrar dispositivos capaces de reproducir y capturar vídeos de muy alta resolución a altas tasas de frame, estas altas prestaciones suponen una mayor complejidad en los procesos de tratamiento de vídeo debido a la gran cantidad de datos que contienen. En este contexto, nos encontramos con varios problemas como son la imposibilidad de transmitir vídeo en tiempo real ya que se necesitaría un ancho de banda inasumible y la dificultad de almacenamiento en memoria que siempre es limitada.

Con el fin de superar las limitaciones anteriores, se han desarrollado a lo largo de los años diferentes estándares de codificación de vídeo que tratan de adaptarse a las necesidades de cada momento. De manera muy general, los codificadores de vídeo comprimen la información para que pueda ser almacenada o transmitida ocupando el mínimo espacio posible. Como ejemplo, plataformas como Netflix utilizan el códec de compresión VP9 de Google para descargar películas y series que no ocupen demasiado y poder visualizarlas offline en cualquier dispositivo. Para conseguir dicha compresión, los codificadores aprovechan la alta redundancia de las secuencias de vídeo tanto en el dominio espacial como temporal, de manera que eliminando dicha información redundante, se consigue codificar de manera óptima el contenido de vídeo. Por tanto, debido a la gran cantidad de recursos requeridos y el consecuente aumento en la complejidad y el tiempo de procesado, en esta tesis se investiga el uso de aceleradores hardware basados en FPGAs sobre las partes más complejas y que requieren más tiempo de procesado en los codificadores de vídeo.

En primer lugar, se ha diseñado un acelerador hardware para el cómputo de la estimación de movimento de un codificador de video HEVC. En este caso, el trabajo se ha centrado en el último estándar de codificación de vídeo HEVC, el cual muestra la mejor eficiencia de compresión respecto a sus predecesores. Al igual que en estándares anteriores, la eliminación de la redundancia temporal demanda un coste computacional abrumador, especialmente en secuencias de video de alta resolución. Por ello, el bloque de estimación de movimiento del codificador (predicción Inter) es uno de los módulos más críticos en la compresión de vídeo. Partiendo de este contexto, nuestro diseño se basa en la implementación de la estimación de movimiento de un codificador HEVC sobre FPGA, proponiendo dos técnicas novedosas, tanto en el árbol de sumadores para el cálculo de la estimación, como en el orden de lectura de memoria. Los resultados muestran que utilizando nuestro módulo hardware de estimación de movimiento, un codificador HEVC es capaz de codificar secuencias de muy alta resolución a tasas de frame más altas que las que se requieren a tiempo real.

En segundo lugar, se presenta una implentación hardware sobre FPGA de un codec muy sencillo llamado MPCM basado en la eliminación de la redundancia espacial (predicción Intra). Este codec presenta las mismas ventajas que la codificación PCM, reduciendo considerablemente el ancho de banda necesario y manteniendo la misma calidad de imagen. Los resultados experimentales obtenidos demuestran que nuestra implementación hardware permite la grabación continua a muy buena calidad en cámaras actuales de alta velocidad.

Esta tesis se ha realizado bajo la modalidad de presentación de tesis doctorales con un conjunto de publicaciones recogida en la normativa de la Universidad Miguel Hernández de Elche. En cumplimiento de dicha normativa se han incorporado las publicaciones que la componen como anexo y se han incluído las secciones correspondientes a la descripción general de la investigación, el resumen global de los resultados obtenidos y las conclusiones finales.

# Contents

| 1   | Intr   | oduction                                                                                                                                                                                            | 1  |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 1.1    | Motivation                                                                                                                                                                                          | 2  |

|     | 1.2    | Objectives                                                                                                                                                                                          | 7  |

|     | 1.3    | Articles                                                                                                                                                                                            | 8  |

|     |        | <ul> <li>1.3.1 Design and implementation of an efficient hardware integer motion estimator for an HEVC video encoder .</li> <li>1.3.2 MPCM: a hardware coder for super slow motion video</li> </ul> | 10 |

|     |        | sequences                                                                                                                                                                                           | 13 |

| 2   | Rese   | earch results                                                                                                                                                                                       | 15 |

|     | 2.1    | Materials and methods                                                                                                                                                                               | 16 |

|     | 2.2    | Results                                                                                                                                                                                             | 19 |

|     |        | Results                                                                                                                                                                                             | 19 |

|     |        | 2.2.1.1 Prototype implementation                                                                                                                                                                    | 27 |

|     |        | 2.2.2 Image coding acceleration                                                                                                                                                                     | 32 |

| 3   | Con    | clusions and future work                                                                                                                                                                            | 39 |

|     | 3.1    | Conclusions and future research lines                                                                                                                                                               | 40 |

|     | 3.2    | Conclusiones y futuras líneas de investigación                                                                                                                                                      | 41 |

|     | 3.3    | Other publications                                                                                                                                                                                  | 43 |

| Bil | bliogi | raphy                                                                                                                                                                                               | 45 |

| I   | Acro   | onyms                                                                                                                                                                                               | 49 |

| II  | Arti   | cles                                                                                                                                                                                                | 53 |

# **List of Figures**

| 1.1  | Simplified view of a Xilinx logic cell                               | 6  |

|------|----------------------------------------------------------------------|----|

| 1.2  | Architecture of a typical FPGA                                       | 7  |

| 1.3  | CU splitting modes into Prediction Units in inter prediction         | 11 |

| 1.4  | HEVC quad-tree structure: CUs and Prediction Units relationship      | 11 |

| 1.5  | HEVC Prediction Units in a frame                                     | 12 |

| 2.1  | General structure IME architecture                                   | 20 |

| 2.2  | Scan order of the search area                                        | 21 |

| 2.3  | Structure of SAD Tree Block                                          | 21 |

| 2.4  | Pipeline process of the proposed architecture                        | 22 |

| 2.5  | R/D performance for different CTU and search area sizes for          |    |

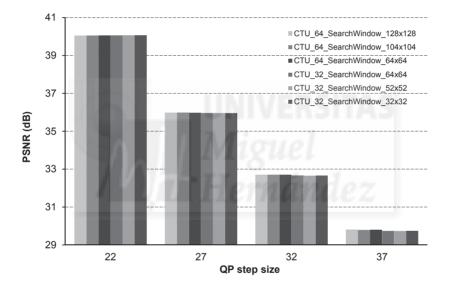

|      | the RaceHorses sequence                                              | 26 |

| 2.6  | Top-level hardware architecture                                      | 28 |

| 2.7  | Percentage of software reference encoding time required for          |    |

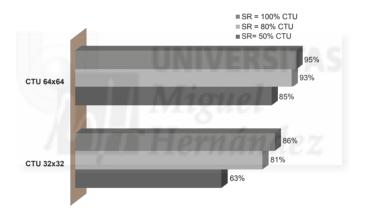

|      | SAD module with a FS strategy.                                       | 28 |

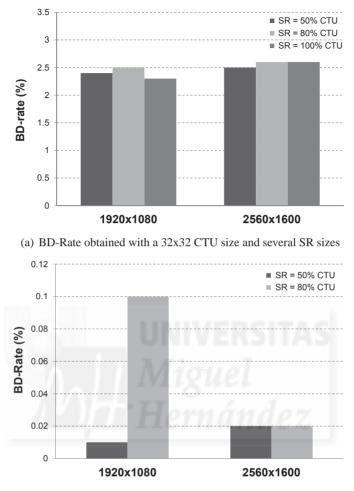

| 2.8  | BD-Rate values with (a) 32x32, and (b) 64x64 CTU sizes               | 29 |

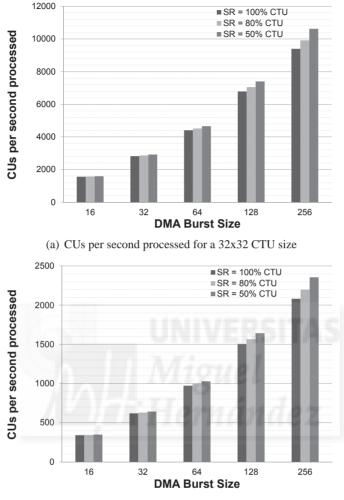

| 2.9  | CUs per second processed for each DMA burst size with our            |    |

|      | proposed SAD HEVC module                                             | 30 |

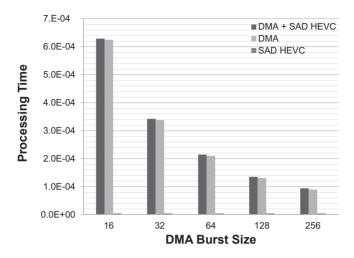

| 2.10 | Hardware Processing Time for different DMA burst sizes               | 31 |

|      | Hardware gain (x times) facing software FS and software DS           |    |

|      | strategies                                                           | 31 |

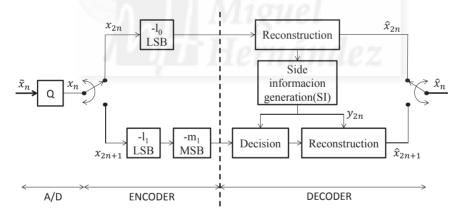

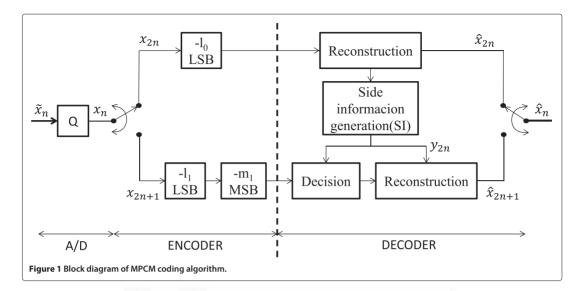

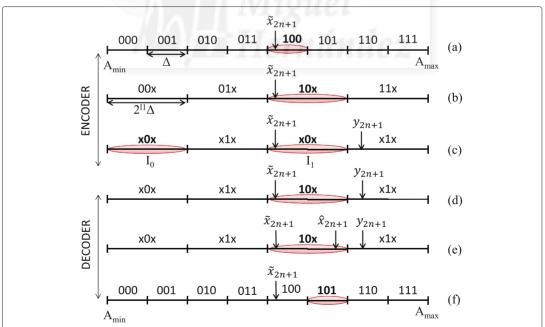

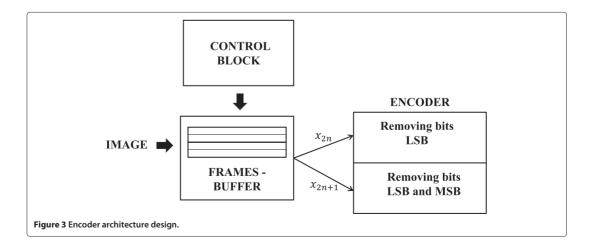

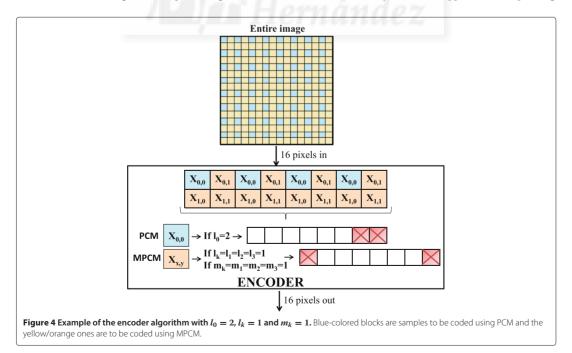

| 2.12 | Block diagram of MPCM coding algorithm                               | 32 |

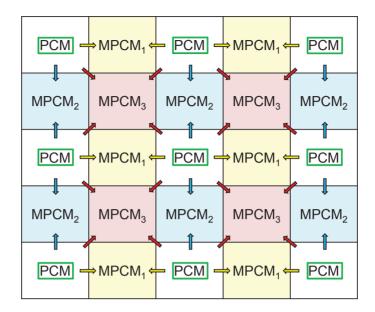

|      | Samples in $S_0$ required to predict samples in $S_1$ when $N = 4$ . |    |

|      | $PCM \in S_0; MPCM_1, MPCM_2, MPCM_3 \in S_1 \dots \dots$            | 33 |

| 2.14 | PSNR as a function of bitrate using image Tractor encoded with       |    |

|      | MPCM and PCM.                                                        | 35 |

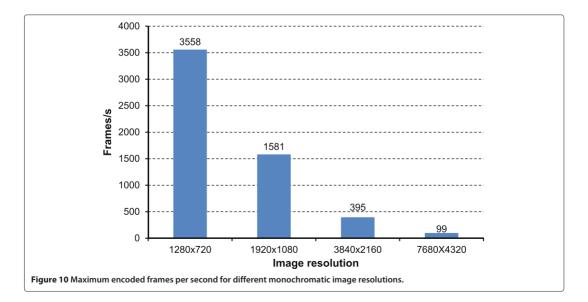

| 2.16 | Maximum encoded frames per second for different monochro-            |    |

| 0    | matic image resolutions                                              | 37 |

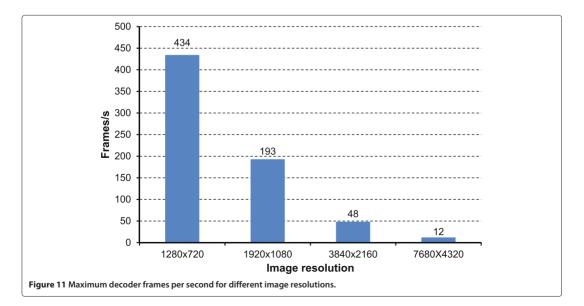

| 2.17 | Maximum decoder frames per second for different image reso-          | 57 |

| 2.17 | lutions                                                              | 37 |

|      |                                                                      | 51 |

# **List of Tables**

| 2.1  | Video sequences used during the research                       | 17 |

|------|----------------------------------------------------------------|----|

| 2.2  | Images used during the research                                | 18 |

| 2.3  | FPGAs Feature Summary                                          | 18 |

| 2.4  | Throughput for different configurations in Virtex-7            | 22 |

| 2.5  | Utilization resources for 64x64 CTU implementation in Virtex-7 | 23 |

| 2.6  | Utilization resources for 32x32 CTU implementation in Virtex-7 | 23 |

| 2.7  | Comparison of the proposed architecture with state-of-the-art  |    |

|      | works                                                          | 24 |

| 2.8  | Time profile of the IME HEVC for a 64x64 CTU with video        |    |

|      | sequences Race Horses(s1), Basketball Drive(s2), and People    |    |

|      | <i>On Street</i> (s3)                                          | 25 |

| 2.9  | Time profile of the IME HEVC for a 32x32 CTU with video        |    |

|      | sequences Race Horses(s1), Basketball Drive(s2), and People    |    |

|      | <i>On Street</i> (s3)                                          | 26 |

| 2.10 | Average CTU IME time with 2xCTU search area size               | 27 |

| 2.11 | PSNR values for all tested images for a given bit-rate         | 34 |

|      |                                                                |    |

### **Chapter 1**

# Introduction

#### Contents

|     | Motivation                                                                                    | 2  |

|-----|-----------------------------------------------------------------------------------------------|----|

| 1.3 | Articles                                                                                      | 8  |

|     | 1.3.1 Design and implementation of an efficient hardware integer motion estimator for an HEVC |    |

|     | video encoder11.3.2MPCM: a hardware coder for super slow motion                               | .0 |

|     | video sequences 1                                                                             | 3  |

#### **1.1 Motivation**

Activities carried out in this dissertation are directly related with the design of efficient image and video coders. These research activities are motivated by the interest and impact of the latest new video compression standards to meet the market multimedia trends, such as very high definition video content (resolutions 4K and 8K). Therefore, this work has been focused on the FPGA hardware implementations of image and video coders that are able to operate at very high-speeds with High Definition (HD) and UHD formats.

A video signal is represented as a sequence of frames of pixels. There exists a vast amount of redundant information that can be eliminated with video compression technology so that transmission and storage becomes more efficient. The similarity among different frames is called temporal redundancy, whereas the homogeneity inside single frames is know as spatial redundancy. Most video codecs use both spatial and temporal compression. In order to facilitate interoperability between compression at the video producing source and decompression at the consumption end, several generations of video coding standards have been defined and adapted. In this way, big companies use these video coding standards since they can give a significant technical and commercial edge to a product, by providing better image quality, greater reliability and/or more flexibility than competing solutions. At the moment, for low-end applications, software solutions are needed. [1]

Taking into account this scenario, the need to design hardware architectures that accelerate video coding arises in order to alleviate the computational complexity of current encoders, reaching high frame rates at ultra high resolutions. Therefore, now we will explain in a more detailed way, the most relevant aspects of both video coding and hardware design with FPGAs.

On the one hand, regarding video coding standards, video coding standards are mainly developed by two world organizations ISO/IEC MPEG and ITU-T VCEG [2, 3].

Three of the ITU-T VCEG video coding standards are the following:

• ITU-T H.120 *Codecs for videoconferencing using primary digital group transmission* was the first international standard for digital video compression. It was originally developed in 1984 and substantially revised in 1988, including such pioneering developments as motion-compensated inter-frame coding.

- ITU-T H.261 *Video codec for audiovisual services at p x 64 kbit/s* was the first commercially-successful digital video coding standard, and introduced the modern architecture of hybrid block-based video coding technology.

- ITU-T H.263 *Video coding for low bit rate communication* provided substantial improvements for real-time video coding communication, and was deployed in mobile devices as well as video conferencing systems.

Anothers video coding standards have been developed by ISO/IEC (also known as MPEG), such as:

- MPEG-1 *Coding reasonable quality images and sound at low bit rates* was established in 1992. MPEG-1 can be encoded at bit rates as high as 4-5Mbits/sec, but the strength of MPEG-1 is its high compression ratio with relatively high quality. MPEG-1 is also used to transmit video over digital telephone networks. MPEG-1 audio compression is more popularly known as MP3 and has revolutionized the digital music domain.

- MPEG-2 *Higher quality images at higher bit rates* was developed in 1994. MPEG-2 is the standard specified for DVD. The primary users of MPEG-2 are broadcast and cable companies who demand broadcast quality digital video and utilize satellite transponders and cable networks for delivery of cable television and direct broadcast satellite.

- MPEG-4 Coding of audio-visual objects was introduced in 1998. MPEG-4 include compression of Audio and Visual (AV) data for web (streaming media) and CD distribution, voice (telephone, videophone) and broadcast television applications. MPEG-4 absorbs many of the features of MPEG-1 and MPEG-2 and other related standards, adding new features such as extended Virtual Reality Modeling Language (VRML) support for 3D rendering, object-oriented composite files (including audio, video and VRML objects). support for externally specified Digital Rights Management and various types of interactivity. Initially, MPEG-4 was aimed primarily at low bit-rate video communications; however, its scope as a multimedia coding standard was later expanded. MPEG-4 is efficient across a variety of bit-rates ranging from a few kilobits per second to tens of megabits per second. MPEG-4 provides the following functions: improved coding efficiency over MPEG-2, ability to encode mixed media data (video, audio, speech), error resilience to enable robust transmission, and ability to interact with the audio-visual scene generated at the receiver.

- MPEG-7 *Multimedia Content Description Interface*. MPEG-7 is the latest proposal in the family of MPEG standards and will be formalized into a

standard by September 2000. MPEG-7 will be a standardized description of various types of multimedia information. MPEG-7 will not replace MPEG-1, MPEG-2 or MPEG-4. It is intended to provide complementary functionality to these other MPEG standards, representing information about the content, not the content itself (the bits about the bits). This functionality is the standardization of multimedia content descriptions.

Three other video coding have been developed collaboratively by both ISO/IEC MPEG and ITU-T VCEG:

- ITU-T H.262 ISO/IEC 13818-2 *Generic coding of moving pictures and associated audio information*. Video is the result of the development under the collaborative team of the ITU-T advanced video coding rapporteur group and MPEG. It ushered in the era of digital television as it is known today.

- ITU-T H.264 ISO/IEC 14496-10 Advanced video coding for generic audiovisual services is the result of the development under the collaborative team known as the JVT. It has become the dominant video coding technology world-wide and now accounts for roughly half of all communication network traffic world-wide (and over 80% of Internet video).

- ITU-T H.265 ISO/IEC 23008-2 *High efficiency video coding (HEVC)* is the result of the development under the collaborative team known as the JCT-VC. It is now emerging as a substantial advance over prior designs to ease pressure on global networks and usher in an era of ultra-high definition television.

Any codec that is compatible with H.261/263/264/265 or MPEGs (1/2/4) has to implement a similar set of basic coding and decoding functions (although there are many differences of detail between the standards and their actual implementations). The model that these standards have in common, is often described as a hybrid DPCM/DCT codec.

Hybrid video coding is a scheme used by many video *codecs* (coder-decoder) that includes both *predictive coding* and *transform coding* in the compression and decompression processes. A hybrid video coding scheme consists of several stages. First, it makes use of the temporal or spatial redundancy present in a video sequence in order to *predict* a region of a frame, and this prediction is subtracted from the region that is currently being encoded. Then the resulting coefficients are quantized (lossy compression). Finally, the quantized coefficients are ordered and entropy coded.

In the encoding process, each frame is divided into small square regions or blocks. These blocks can be encoded using one of three modes: (a) without any prediction, (b) using spatial prediction, or (c) using temporal prediction. *Spatial prediction* exploits redundancy within a frame. In order to encode a block, it uses previously encoded regions of the same frame to search for pixel information that is similar to that block in order to create a candidate. Then, this candidate is subtracted from the current block and thus we obtain the residuum of the prediction. This method is also called *intra*-frame prediction. The article *MPCM: a hardware coder for super slow motion video sequences* shows the hardware design of an MPCM encoding that addresses the elimination of spatial redundancy in an image or frame in an efficient way to achieve very high frame rates.

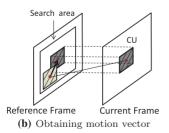

Temporal prediction uses previously encoded frames to estimate a block candidate by means of the search of a similar block in other frames (called reference frames), which have been previously encoded, decoded, and stored in a buffer. It exploits temporal redundancy, taking advantage of the fact that nearby frames usually contain blocks that are very similar to the current block and so the residuum of the compensation is close to zero. This method is also called *inter*-frame prediction. The article *Design and implementation of an efficient hardware integer motion estimator for an HEVC video encoder* shows the implementation of the HEVC motion estimator block in hardware which deals with the inter-frame prediction.

On the other hand, we have used FPGA technology, since it encourages design reuse and can greatly enhance the upgradability of digital systems. A FPGA is a semiconductor device that can be programmed after manufacture to perform a specific application design, typically specified as a digital logic system [4]. They are being used for many real-life applications including communications, encryption, video image processing, medical imaging, network security and numerical computations. Specifically, the programmability of FPGAs is particularly useful for highly flexible encoding systems that can accommodate a multitude of existing standards as well as the emergence of new ones.

FPGAs can potentially approach the execution speed of application specific hardware with the rapid programming time of microprocessors. In recent years, the size of FPGAs has followed Moore's law: the number of logic gate doubles every 18 months. FPGAs can exploit improvements following Moore's law better than microprocessors because of their simpler and more regular structure.

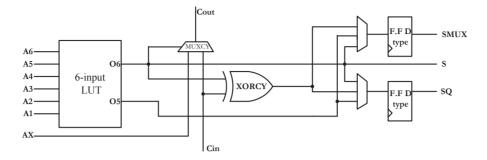

The two major FPGA vendors are Altera and Xilinx. The fundamental building block of Xilinx FPGAs is the logic cell. In current Xilinx FPGA families, a logic cell comprises a 6-input Look-up table (LUT), two

Figure 1.1. Simplified view of a Xilinx logic cell

multiplexers, and two registers. LUTs can be configured as either one 6-input LUT (64-bit Read Only Memorys (ROMs)) with one output, or as two 5-input LUTs (32-bit ROMs) with separate outputs but common addresses or logic inputs. Each LUT output can optionally be registered in a flip-flop. A simplified view of a logic cell is depicted in Figure 1.1.

Four LUTs and their eight flip-flops as well as multiplexers and arithmetic carry logic form a slice, and two slices form a Configurable Logic Block (CLB). Four of the eight flip-flops per slice (one flip-flop per LUT) can optionally be configured as latches. Between 25-50% of all slices can also use their LUTs as distributed 64-bit RAM or as 32-bit shift registers (SRL32) or as two SRL16s. Modern synthesis tools take advantage of these highly efficient logic, arithmetic, and memory features. Futhermore, recent generation reconfigurable hardware has a large amount of resources, for instance, the Xilinx Virtex UltraScale XCVU440 has 5,065,920 Flip-Flops and 2,532,960 LUTs.

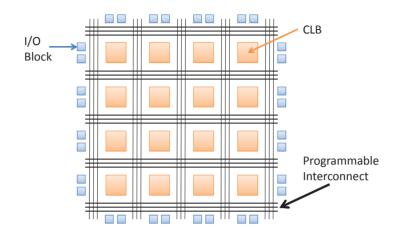

The architecture of a typical FPGA is illustrated in Figure 1.2. In general, an FPGA will have an array CLBs, programmable wires, and programmable switches to realize any function out of the logic blocks and implement any interconnection topology. Programming is done using of the many popular technologies such as SRAM cells, antifuses, EPROM transistors and EEPROM transistors. In addition to logic blocks, nowadays FPGAs such as Xilinx Virtex-7 devices contain embedded hardware elements for memory, multiplication, multiply-and-add and a number of hard microprocessor cores (such as ARM Cortex-9 or the IBM PowerPC), and even, they are part of a System-On-Chip (SoC) embedded with external memory and hard peripherals such as Xilinx Zynq-7000 families.

The long IC fabrication time is completely eliminated for these devices and design realization times are only a few hours. The idea of

Figure 1.2. Architecture of a typical FPGA

user-programmability is very exciting, most ASIC vendors now prefer FPGAs for low cost prototyping for fine tuning of designs before fabrication. Also, from a marketing point of view, the FPGA technology allows quick product announcements, which is commercially attractive [5].

During the development of this thesis, several FPGAs and SoCs of Xilinx have been used. Xilinx devices are now much larger and come with a variety of new technology, including 144 kb UltraRAM, DSP48E2, high-speed transceivers up to 28 Gigabits (Gbs) Input-Output (I/O) interfaces, hardened microprocessors and peripherals, analog mixed signal, and more. These larger and more complex devices create multidimensional design challenges, but handled correctly, they can achieve faster time-to-market and increase productivity.

#### 1.2 Objectives

The general objectives of this thesis have been the following:

- Design of efficient hardware image and video encoders.

- Develop prototypes of FPGA accelerators that allows high-speed video coding at high-definition formats.

Based on the previous general objectives, the specific objectives of this work are detailed below:

- Study, design and implementation of a fast and simple hardware encoder that allows continuous capture and coding in real time with ultra high-speed cameras.

- Analysis of the computational complexity of nowadays video encoders.

- Design and implementation of a hardware integer motion estimation module for HEVC video encoder. This new hardware module will speed up its coding process and eliminate its high computational cost.

- Study and evaluation of the balance between the throughput, compression rates, image quality, the hardware complexity and the FPGA usage.

#### **1.3** Articles

This dissertation has been carried out in the modality of a doctoral thesis presented with a set of publications. According to the Internal Regulations of the Miguel Hernandez University for the presentation of doctoral theses with a set of publications, this dissertation includes a general introduction where the work done is presented and justified. It also incorporates a global summary with the results obtained, their discussion and the final conclusions, in both languages English and Spanish. Finally, an annex with the publications presented in their original language is attached.

The publications presented in this thesis are:

Design and implementation of an efficient hardware integer motion estimator for an HEVC video encoder

Estefania Alcocer, Roberto Gutierrez, Otoniel Lopez-Granado, and Manuel P. Malumbres

Journal of Real-Time Image Processing. Springer Verlag Berlin Heidelberg 2016

Impact factor: 1.564

Category Name: ENGINEERING, ELECTRICAL & ELECTRONIC

Quartile in Category: Q2 ISSN 1861-8219 http://dx.doi.org/10.1007/s11554-016-0572-4

MPCM: a hardware coder for super slow motion video sequences

Estefania Alcocer, Otoniel Lopez-Granado, Roberto Gutierrez, and Manuel

P. Malumbres

EURASIP Journal on Advances in Signal Processing 2013. Springer Open

Journal

Impact factor: 0.808

Category Name: ENGINEERING, ELECTRICAL & ELECTRONIC

Quartile in Category: Q3

ISSN 1687-6180

http://dx.doi.org/10.1186/1687-6180-2013-142

The publications explained below focus on the design of hardware systems that perform the computationally costliest parts of a codec in both video and image video coding in order to achive ultra-fast encoding at high frame rates for high-resolution formats.

On the one hand, the first publication deals with hardware Integer Motion Estimation (IME) for an HEVC video encoder. HEVC standard is the most recent joint video project of the ITU-T VCEG and ISO/IEC MPEG standardization organizations, working together in a partnership known as the Joint Collaborative Team on Video Coding (JCT-VC) [6]. HEVC has been designed to cope with new video services, working with higher video resolutions and adapting its design to allow the use of parallel processing techniques. It can compress video about twice as much as its predecessor, H264/Advanced Video Coding (AVC), without sacrificing quality, but increasing the computational complexity. As in previous standards, ME is one of the encoder critical blocks to achieve significant compression gains, but it demands an overwhelming complexity cost to accurately remove video temporal redundancy. The purpose of this work is the implementation of a HEVC ME block in hardware in order to reduce the overall video encoding time and to achieve real-time encoding for high-resolution videos.

On the other hand, the second article is based on the hardware implementation of a very simple codec called MPCM, whose coding/decoding process of each pixel is based on the prediction and interpolation of neighboring pixels of the same frame. The purpose of this work is to take advantage of a codification as simple as possible to capture high resolution videos at ultra high frame rates.

## **1.3.1** Design and implementation of an efficient hardware integer motion estimator for an HEVC video encoder

In this work, a design of a new hardware architecture which perform IME computation in a fast and accurate way is proposed, in order to significantly reduce the computation cost of the overall encoder.

The ME technique is based on the similarity between adjacent video frames, predicting the current frame based on a previous or subsequent reference frame in order of appearance. The Motion Vector (MV) represents the translational movement of a picture area in the current frame compared to its position in the reference frame.

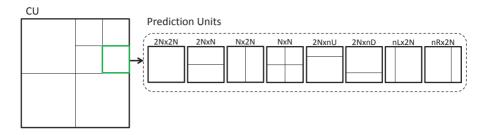

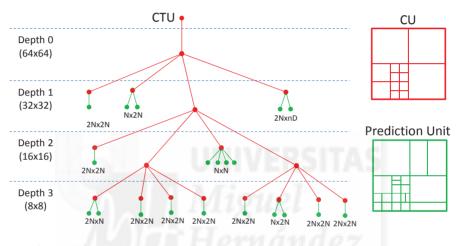

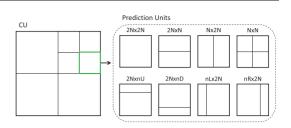

In the HEVC video coding standard, each frame is partitioned into Coding Tree Units (CTUs) which cover a rectangular picture area of LxL samples. The value of L may be equal to 16, 32, or 64 as determined by an encoded syntax element specified in the Sequence Parameter Set (SPS). The larger size typically enables better compression, particularly beneficial when encoding high-resolution video content. The CTU is the basic processing unit used in the standard that can be directly used Coding Units (CUs) or can be further partitioned into multiple CUs. The partitioning is achieved using tree structures. The CTU contains a quadtree syntax that allows for splitting the CUs to a selected appropriate size based on the signal characteristics of the region that is covered by the CTU. The quadtree splitting process can be iterated until the size reaches the minimum allowed that is selected by the encoder using syntax in the SPS and is always 8x8 samples or larger. The prediction mode for the CU is signaled as being intra or inter, according to whether it uses intra-picture (spatial) prediction or inter-picture (temporal) prediction. When the prediction mode is signaled as intra, the CU can be split into four quadrants that each have their own intra prediction mode, from the CU size until 4x4 blocks. When the prediction mode is signaled as inter, that is the case which concerns us, it is specified whether CUs are split into one, two, or four prediction units. When a CU is split into four prediction units, each one covers a quadrant of the CU. When a CU is split into two prediction units, various types of this splitting are possible. The partitioning possibilities for inter-predicted CUs are depicted in Figure 1.3.

The first four partitions illustrate the cases of not splitting the CU of size 2Nx2N, of splitting the CU into two prediction units of size 2NxN or Nx2N, or splitting it into four of size NxN. The next four partition types in Figure 1.3 are referred to as Asymmetric Motion Partitions (AMPs). One prediction unit of the asymmetric partition has the height or width 2N/4 and width or height 2N, respectively, and the other prediction unit fills the rest of the CU by

Figure 1.3. CU splitting modes into Prediction Units in inter prediction

Figure 1.4. HEVC quad-tree structure: CUs and Prediction Units relationship

having a height or width of 3x(2N)/4 and width or height 2N. Each inter-coded prediction unit is assigned one or two motion vectors and reference picture indices. To minimize worst-case memory bandwidth, the minimum prediction unit size is restricted to 4x8 or 8x4. The quadtree syntax of the CTU, in which CUs and prediction units relationship is shown, is represented in Figure 1.4. In addition, as a real example, the Figure 1.5 shows the partitioning that is performed in a frame of the video sequence RaceHorses during the HEVC Motion Estimation.

Finally, in the HEVC inter-prediction process, the total number of different partitions for a 64x64 CTU is more than 600, and for each of these partitions, the HEVC encoder performs one ME process to determine the best CU partitions in terms of bit rate and video quality. In this way, in this publication a high-performance IME hardware unit in HEVC that provides the minimum SADs and associated MVs of all possible partitions from a 64x64 CTU for inter-prediction is presented, exploiting parallelism in an efficient way, by

Figure 1.5. HEVC Prediction Units in a frame

means of a Full Search (FS) algorithm which exhaustively finds motion for all prediction unit blocks at every single point of the established search area since provides computational regularity and excellent video quality. In order to perform this implementation, the Xilinx FPGA Virtex-7 was used.

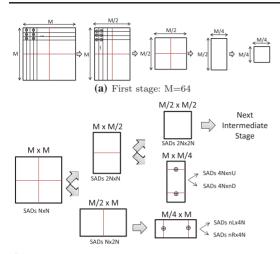

Focusing on the computation blocks of the hardware ME proposal, we present both innovative techniques: a new SAD adder tree structure, and a new memory scan order. Firstly, we designed a new SAD adder tree structure to perform the additions at the first level of the tree, starting from the maximum size of the CTU, and halving the amount of additions at the next tree levels. With our proposal, we took advantage of the resources provided by the FPGA, obtaining the minimum possible latency when calculating SADs of all levels and partitions for a CTU. Secondly, regarding the new memory scan order, a series of reconfigurable shift registers and processing elements are responsible for storing the necessary pixels of both reference and current frames, keeping them always available for calculating the SADs and MVs of a CTU. With our system, we avoid external memory accesses since available data are highly reused by reconfiguring the displacement in a more efficient way.

The architecture described above was modeled in VHDL, and was synthesized, simulated, and implemented on the Xilinx FPGA, Virtex-7 XC7VX550T-3FFG1158 [7]. The experiments were performed using different configurations of both search area sizes (128x128, 104x104, 64x64, 52x52,

and 32x32) and CTU sizes (64x64 and 32x32). The correctness of this design was tested and verified with the HEVC HM 14 reference model [8] working with the main profile and low-delay configuration mode, using three video sequences from the HEVC common conditions video set with different resolutions and frame rates.

First, the throughput for different configurations of CTU and search area sizes in the Virtex 7 FPGA technology was assessed, showing frequency (clock), latency, and the system throughput in terms of the maximum frame rate under different video formats (1080p, 2K, and 4K). For these configurations, the resources used on the Virtex-7 FPGA were also shown. Futhermore, our hardware design was compared with other state-of-art architectures which perform the same functionality under FPGA technology. Finally, the integration of our IME FPGA-based accelerator was analyzed in terms of speed-up and was observed how the different CTU and search area size configurations impact on the R/D performance of the HEVC encoder, with regard to the HEVC reference software. The results of this research are detailed in section 2.2.1.

# **1.3.2** MPCM: a hardware coder for super slow motion video sequences

In this work, a fast FPGA implementation of a simple codec called MPCM is proposed. This hardware codec is intended to allow current high-speed cameras to capture in a continuous manner.

Source coding algorithms must be extremely simple for new comercial high-speed cameras that capture high-resolution videos at frame rates up to 10,000 frames/second. Most of ultahigh-speed cameras store the captured images in a fast Synchronous Dynamic Random Access Memory (SDRAM) module of up to 64 GB [9, 10, 11, 12]. This approach of using fast SDRAM memory as video storage is feasible since the memory bandwidth is high enough, but when memory is run out, the camera stops recording and needs to save the stored video to a secondary storage in raw or compressed format. This is a limitation because depending on the capturing resolution of the camera, only a few seconds could be recorded in the Random Access Memory (RAM) module, and so continuous capturing is not possible. For these reasons, many times high-resolution videos at high frame rates are recorded or transmitted using PCM (raw video) since is the simplest technique [13]. PCM coding presents several advantageous properties, for instance, direct processing, random access, and rate scalability. However, the high bit rate of raw video can make its transmission or storage difficult. The huge

amount of data of the resulting uncompressed image/video needs to be processed to guarantee its transmission or storage, being a really challenging task. Thus, the internal communication bus may not be fast enough to transfer the video out of the camera, or the writing speed of the storage device may not be high enough to save the video [14]. So as to overcome these restrictions, it would be of interest both, to reduce the video storage requirements by means of hardware encoders that fulfill the application requirements such as high frame rate and ultra-high-definition video formats, and to consider a coding algorithm which had properties similar to those of PCM (low complexity, random access, and scalability) with a better coding efficiency.

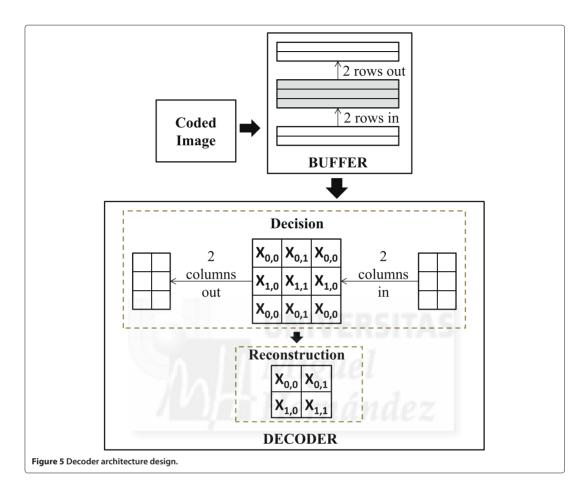

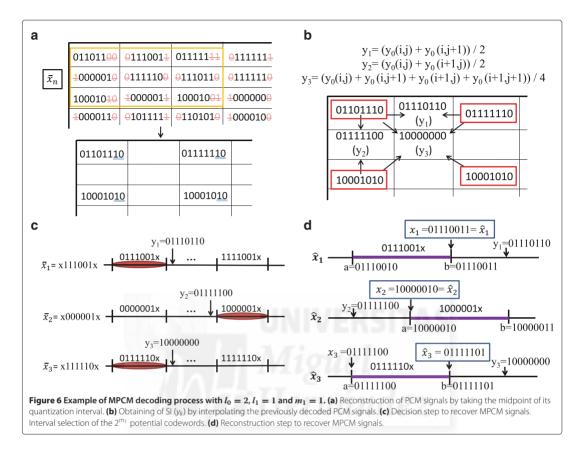

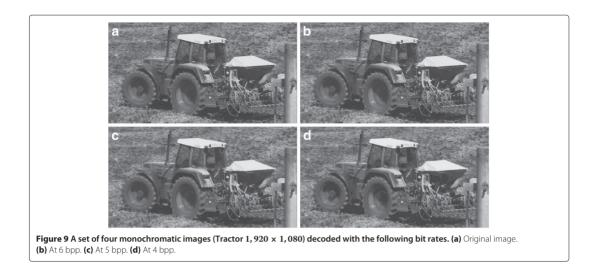

MPCM [15] image coder is able to reduce the rate of the PCM signal in a very simple way without losing the advantages provided by PCM coding, as prososed in [16]. In this algorithm, MPCM encoder removes certain bits from each pixel value which represents a very simple processing, in order to encode an image. At the decoder side, where the bits that were removed from each pixel will be predicted by using its codeword (remaining bits of a pixel) and Side Information (SI) that the decoder computes by interpolating the previously decoded pixels. In this work, a hardware codec based on MPCM on a XC7Z020-1CLG484CES Xilinx FPGA device was implemented. Both encoder and decoder architecture designs were tested and validated.

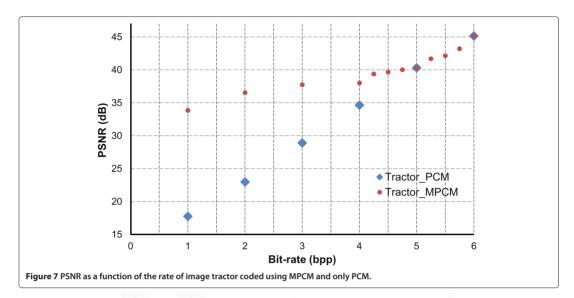

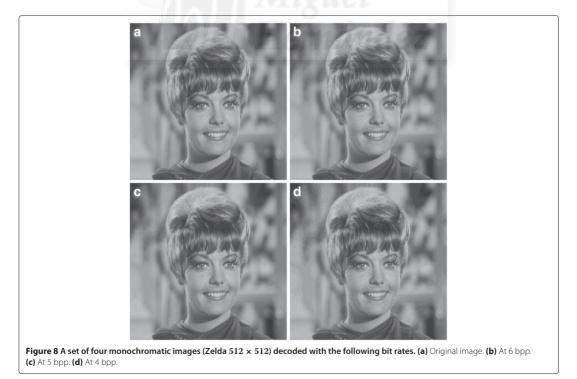

Regarding results, an evaluation of the complete system was performed in terms of Peak Signal-to-Noise Ratio (PSNR), encoding/decoding times, board area usage, maximum frame rate, and resulting speed-ups when compared to a CPU sequential algorithm. The results of this research are detailed in section 2.2.2.

### **Chapter 2**

# **Research results**

#### Contents

| 2.1 | Materials and methods |                                  |  |  |  |  |  |

|-----|-----------------------|----------------------------------|--|--|--|--|--|

| 2.2 | Results               |                                  |  |  |  |  |  |

|     | 2.2.1                 | Video coding acceleration        |  |  |  |  |  |

|     |                       | 2.2.1.1 Prototype implementation |  |  |  |  |  |

|     | 2.2.2                 | Image coding acceleration        |  |  |  |  |  |

#### 2.1 Materials and methods

The resources described below are those used to carry out the research of this thesis:

#### • Vivado Design Suite of Xilinx

This tool suite is intended to increase the overall productivity for designing, integrating, and implementing systems using the Xilinx UltraScale and 7 series devices, Zyng UltraScale + MPSoC device, and Zyng-7000 All Programmable (AP) SoC [17]. It includes place and route tools that analytically optimize multiple and concurrent design metrics, such as timing, congestion, total wire length, utilization and power. It replaces all of the ISE Design Suite point tools. Vivado introduces the concept of opening designs in memory. Opening a design effectively loads the design netlist at that particular stage of the design flow, assigns the constraints to the design, and applies the design to the target device. This allows to visualize and interact with the design at each design stage and it enables to open designs after Register-Transfer Level (RTL) elaboration, synthesis. and implementation. It can be made changes to constraints, logic or device configuration, and implementation results, as well using design checkpoints to save the current state of any design. A design checkpoint is a snapshot of the design at any stage of the design process that includes the netlist, constraints, and implementation results. Vivado automatically creates design checkpoints at each stage of the flow that can be opened and analyzed.

#### • ISE Design Suite 14 of Xilinx

This tool is a predecessor development environment of Vivado Design Suite. Now, Vivavo has replaced this solution. With performances lower than those currently provided by Vivado, ISE supplies a complete solution for logic and connectivity design encompassing the front-to-back base methodology and Intellectual Property (IP).

#### • HEVC reference software

The reference software for HEVC is called HEVC Test Model (HM). This software has been used for the coding of video sequences, specifically the HM-14 version [8]. In the software repository, the configuration files are also included, which have been modified to obtain the different configurations we needed in this work (search algorithm, block sizes, search area, etc.)

#### • Matlab/Simulink

Matlab is a program widely used in engineering to perform technical,

scientific and general purpose calculations. It integrates calculation operations, visualization and programming. In the case of this research, Matlab, with the help of the Simulink application, has been used for the development, modeling, simulation and prototyping of the mathematical algorithms that have been implemented in both image and video coding, in order to verify the reliability of the model implemented in hardware.

### • Software platform

All software tests have been run over an Intel Core i7-3770 CPU 3.40 GHz with 16 GB RAM.

### • Video sequences

The video sequences used for coding shown at Table 2.1 have been selected from the HEVC common conditions [18].

| Video sequence   | Resolution (pixels) | Frame-rate (fps) |

|------------------|---------------------|------------------|

| Racehorses       | 832x480             | 30               |

| ParkScene        | 1920x1080           | 24               |

| Basketball Drive | 1920x1080           | 50               |

| People On Street | 2560x1600           | 30               |

| Traffic          | 2560x1600           | 30               |

Table 2.1. Video sequences used during the research

### • Images

In Table 2.2 we find the set of gray-scale images that have been used in this work, in order to test the image codec. In all of them, each pixel is represented with 8 bits.

### • Virtex-7 FPGA of Xilinx

Virtex-7 FPGAs are optimized for system performance and integration at 28nm and bring best-in-class performance/watt fabric, DSP performance, and I/O bandwidth to your designs. The family is used in an array of applications such as 10G to 100G networking, portable radar, and ASIC Prototyping [7]. At the present work, the XC7VX550T-3FFG1158 device has been used.

### • Zynq-7000 SoC 7Z020 of Xilinx

This product integrates a feature-rich dual-core ARM Cortex-A9 based Processing System (PS) and 28 nm Xilinx Programmable Logic (PL) in a single device. The FPGA included in this device is the

| Resolution (pixels) |

|---------------------|

| 512x512             |

| 1920x1080           |

| 2048x2560           |

| 3840x2160           |

|                     |

Table 2.2. Images used during the research

XC7Z020-1CLG484CES. The ARM Cortex-A9 CPUs are the heart of the PS and includes 1GB DDR3 memory, 16MB Quad SPI Flash, HDMI Video OUT and a rich set of peripheral connectivity interfaces [19].

#### Avnet Zynq-7000 SoC Mini-ITX of Xilinx

It is a complete development platform for designing and verifying applications based on the Xilinx Zynq-7000 All Programmable SoC family. In addition to the Xilinx Zynq-7000 AP SoC XC7Z100 device (XC7Z100-2FFG900), the Zynq Mini-ITX development board features 2 GB DDR3 SDRAM, PCIe Gen2 x16 Root Complex slot (x4 electrical), SATA-III interface, SFP interface, QSPI Flash memory, HDMI interface, LVDS touch panel interface, Audio Codec, a 10/100/1000 Ethernet PHY, a USB 2.0 4-port hub, a microSD card interface, and a USB-UART port [20].

The main features of the 3 FPGAs used (Virtex-7 and the corresponding ones to the two evaluation boards) are detailed in the Table 2.3

| FPGA               | Virtex-7 XC7VX550T | Z-7020 XC7Z020 | Z-7100 XC7Z100 |

|--------------------|--------------------|----------------|----------------|

| LUTs               | 346400             | 53200          | 277400         |

| Flip-flops         | 692800             | 106400         | 554800         |

| BRAM (36Kb Blocks) | 1180               | 140            | 755            |

| DSP                | 2880               | 220            | 2020           |

| Speed Grade        | -3                 | -1             | -2             |

Table 2.3. FPGAs Feature Summary

### 2.2 Results

In this section an overall summary of the results obtained from research on both video and image accelerators has been presented. Implementations of these accelerators have been analyzed in terms of R/D, processing time, board area usage, maximum frame rate, and speed-ups when compared to software algorithms.

#### 2.2.1 Video coding acceleration

As described in Section 1.3.1, a high-performance IME hardware unit in HEVC that provides the minimum SADs and associated MVs has been implemented. The architecture is based on both a new memory scan order and a new adder tree structure, which supports all partitioning modes and allows different configurations, such as (a) the maximum CTU size with values of 64x64 and 32x32, and (b) the size of the search area of the reference frame with values defined as the double size of the CTU, 80% of the double size of the CTU, and the same size as a CTU.

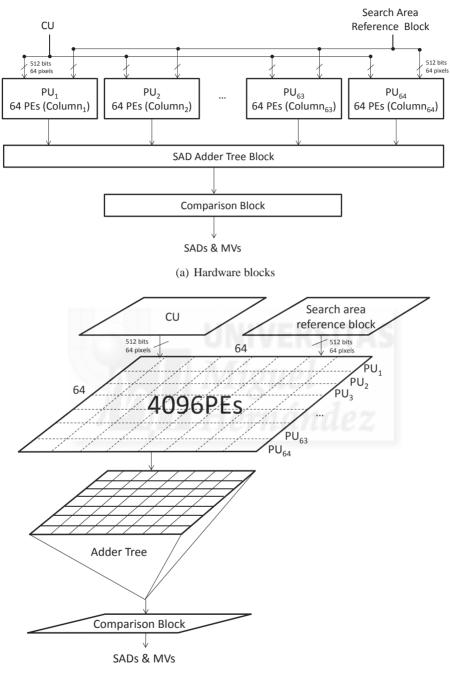

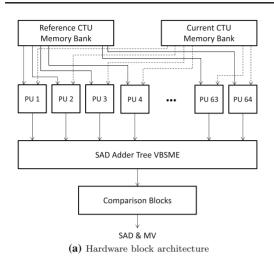

The system is composed of memory areas for current CU and reference search area pixels, 64 Processing Units (PUs), one SAD Adder Tree Block (SATB), and one comparison block that saves the minimum SAD values and their corresponding MVs for all CU partitions. Figure 2.1 shows the structure of hardware IME architecture.

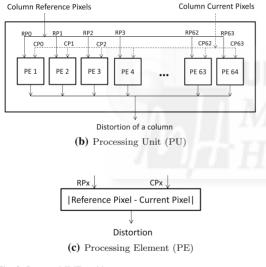

Regarding our new innovative technique about memory scan order, a snake scan order and a reconfigurable data path with 64 propagation registers were adopted in order to provide high data reuse. The snake scan order visits all positions of the search area following a Hamiltonian path composed by consecutive vertical scans with alternating scan directions (the first vertical scan begins from top to bottom, then moves one pixel to the right and starts the next vertical scan in a bottom to up direction, and so on) as illustrated in Figure 2.2.

There are three scanning directions U (upward), D (downward), and R (rightward). The current 64x64 CTU pixels are stored in the Processing Element (PE)s only once (at the beginning). The reference pixels will also be loaded to the PEs but instead of loading from Block Random Access Memory (BRAM), where the pixels belonging to a reference frame area are stored, will be loaded from the shift registers, since they will help us to perform the snake scan order and as a consequence a huge reduction of memory load operations will be achieved.

Figure 2.1. General structure IME architecture

Figure 2.2. Scan order of the search area

Figure 2.3. Structure of SAD Tree Block

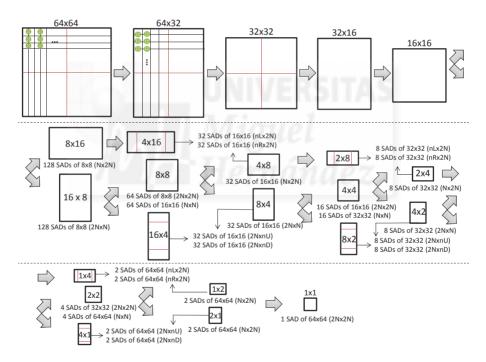

Regarding the second new method, a SATB block which computes the SAD values for all partitions of each 64x64 CTU at every clock cycle has been developed. After receiving the 64x64 distortions from PUs associated to the current search area position, a succession of aggregation stages are performed in this block to compute the corresponding SAD values for all the CTU partitions (a total number of 677), as shown in Figure 2.3.

16462 clock cycles

Figure 2.4. Pipeline process of the proposed architecture

**Table 2.4.** Throughput for different configurations in Virtex-7

| CTU size     | 64x64   | 64x64   | 64x64 | 32x32 | 32x32 | 32x32 |

|--------------|---------|---------|-------|-------|-------|-------|

| Search area  | 128x128 | 104x104 | 64x64 | 64x64 | 52x52 | 32x32 |

| Clock (MHz)  | 247     | 247     | 247   | 318   | 318   | 318   |

| Latency      | 16462   | 10894   | 4174  | 4142  | 2750  | 1070  |

| Fps at 1080p | 32      | 48      | 124   | 39    | 59    | 151   |

| Fps at 2K    | 30      | 45      | 116   | 37    | 55    | 141   |

| Fps at 4K    | 8       | 12      | 30    | 10    | 15    | 37    |

At each stage, all pairs of consecutive columns/rows are added, reducing to half the width/height of the resulting partition. This SAD aggregation process is followed until the last partition size is reached (1x1), ie. the SAD corresponding to the 64x64 partition. At intermediate stages, the SADs of the rest of partitions are stored. Finally, in the proposed architecture, the SATB module delivers 677 SADs of the current CTU block every single clock cycle to the next module, the comparison block.

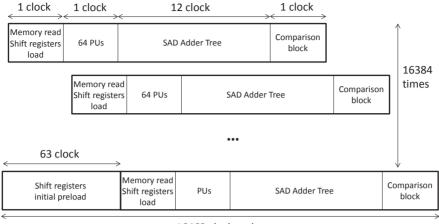

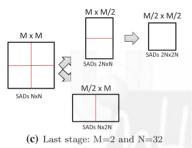

This work was modeled in VHDL, and it was synthesized and simulated on the Xilinx FPGA, Virtex-7 XC7VX550T-3FFG1158. In Figure 2.4, and Tables 2.4, 2.5 and 2.6 the pipeline process with the total latency, the throughput, and the resources used for different configurations are shown, repectively, when our hardware architecture is implemented on the Virtex-7 FPGA described above.

| Resources                    | Flip-Flops     | LUTs           | Memory (kB) |

|------------------------------|----------------|----------------|-------------|

| Memory Read Controller Block | 36657 (25.40%) | 36413 (19.30%) | 36 (100%)   |

| PUs (Distortion computation) | 32768 (22.71%) | 94208 (49.93%) | -           |

| SAD Adder Tree Block (SATB)  | 58727 (40.70%) | 47063 (24.95%) | -           |

| Comparison Block             | 16150 (11.19%) | 10980 (5.82%)  | -           |

| TOTAL                        | 144302         | 188664         | 36          |

Table 2.5. Utilization resources for 64x64 CTU implementation in Virtex-7

Table 2.6. Utilization resources for 32x32 CTU implementation in Virtex-7

| Flip-Flops     | LUTs                                                               | Memory (kB)                                                                                                                                                                                                                                      |

|----------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10155 (27.55%) | 9812 (20.22%)                                                      | 9 (100%)                                                                                                                                                                                                                                         |

| 8192 (22.22%)  | 24541 (50.57%)                                                     | -                                                                                                                                                                                                                                                |

| 14580 (39.55%) | 11445 (23.58%)                                                     | -                                                                                                                                                                                                                                                |

| 3937 (10.68%)  | 2733 (5.63%)                                                       |                                                                                                                                                                                                                                                  |

| 36864          | 48531                                                              | 9                                                                                                                                                                                                                                                |

|                | 10155 (27.55%)<br>8192 (22.22%)<br>14580 (39.55%)<br>3937 (10.68%) | 10155         (27.55%)         9812         (20.22%)           8192         (22.22%)         24541         (50.57%)           14580         (39.55%)         11445         (23.58%)           3937         (10.68%)         2733         (5.63%) |

As shown, in our architecture, with a configuration of a 64x64 CTU size and a search area of 128x128 pixels, the memory reading process and shift registers propagation require only one clock cycle. The PUs use one cycle, the SATB requires twelve additional clock cycles, and the comparison block needs one additional clock cycle. So, the proposed architecture requires 63 clock cycles to perform the initial load of the shift registers, 15 clock cycles to load the pipeline, and then as many clock cycles as positions the search area has. Finally, te whole process is done in 16462 clock cycles, that is, 63 clock cycles for the initial load, plus 15 clock cycles for the full processing in one pixel position, plus 16384 times to repeat the whole process of motion estimation (search window  $128 \times 128$  pixels = 16384 pixels), with only one delay clock cycle in the pipeline. As can be seen in Table 2.4, our design can operate at the frequency of 247 and 318 MHz for a 64x64 CTU and a 32x32 CTU, respectively. Regarding the configuration with maximum sizes, whose latency is 16462 clock cycles, and taking into account the frequency obtained, the encoder carry out the IME process in  $66.65\mu$  seconds, obtaining a throughput of 30 frames per second (fps) at 2K video formats (2K@30fps). The encoder is able to process video in real time for both 1080p and 2K resolutions in all tested configurations, and also with 4K video formats if the search area size is the same as the CTU size. In terms of resources used, the

64x64 CTU size requires near four times more resources, which implies that the use of more resources in the design provides higher throughput, in this case, with a 4:3 relationship, as shown in Tables 2.5 and 2.6.

Futhermore, in Table 2.7, our hardware architecture is compared with other comparable state-of-art architectures implemented on different FPGA platforms for both the 64x64 CTU and the 32x32 CTU size, and different search area sizes.

| Design      | Medhat [21] | Proposal 1 | D'huys [22] | Proposal 2  | Yuan [23]   | Proposal 3  |

|-------------|-------------|------------|-------------|-------------|-------------|-------------|

| CTU size    | 64x64       | 64x64      | 64x64       | 64x64       | 32x32       | 32x32       |

| Search area | 104x104     | 104x104    | 64x64       | 64x64       | 48x48       | 48x48       |

| Technology  | Virtex-7    | Virtex-7   | Virtex-5    | Virtex-5    | Virtex-6    | Virtex-6    |

| Clock (MHz) | 458.7       | 247        | 150         | 159         | 110         | 200         |

| AMP         | No          | Yes        | No          | Yes         | Yes         | Yes         |

| Throughput  | 2K@30fps    | 2K@45fps   | 720p@57fps  | 720p@173fps | 1080p@30fps | 1080p@43fps |

| Flip-Flops  | 39901       | 144302     | 199682      | 178620      | 19744       | 43531       |

| LUTs        | 24957       | 188664     | 210158      | 184288      | 55346       | 45752       |

| Memory (kB) | 44          | 36         | 1229        | 36          | 148         | 9           |

Table 2.7.

Comparison of the proposed architecture with state-of-the-art works

Regarding results for the 64x64 CTU size, Medhat et al. [21] present a parallel SAD block for the HEVC integer-pel FS architecture without supporting AMP modes with a search area of 104x104 pixels. They used the Virtex-7 technology, and their design can operate at the frequency of 458.7 MHz. The operating frequency of our design with the same technology and configurations is almost two times lower. However, our architecture is capable of processing 45 fps at 2K video formats instead of 30 fps as obtained by the proposed design in [21]. Therefore, our proposed architecture is 1.5x as fast as the one proposed in [21] using the same search area size and considering all the AMP partition modes, contrary to [21], where AMP partitions are not calculated. This is due to the fact that our design takes advantage of the minimal latency to perform the same operations as we have an efficient pipeline design. Therefore, our system achieves higher throughput, reaching real-time processing for 2K video resolutions at 45 fps, and being on the way to accomplishing the same goal for 4K video formats, where 12 fps were obtained.

On the other hand, D'huys [22] proposes a reconfigurable design for HEVC motion estimation which can operate at the frequency of 150 MHz. His

architecture is compared with our proposal, setting a common search area size to 64x64 pixels and the Virtex-5 technology. The operation frequency of our proposal is 159 MHz, achieving system throughput of 20 fps at 4K and 75 fps at 2K video formats. Our design significantly improves the performance of the architecture presented in [22], which is able to process a lower resolution video (720p) at 57 fps. If the video resolution is set to 720p, our architecture is capable of processing 173 fps. So, our architecture presents good balance between the maximum frequency and pipeline processing design, taking advantage of the low latency by leveraging all available resources.

Regarding results for the 32x32 CTU size, we show the comparison results between our proposal (implemented on a Virtex-6 FPGA) and the IME design found in [23], both with a search area size of 48x48 pixels. The most significant feature, worthy of attention, is that our proposal can provide a higher operation frequency, achieving throughput of 43 fps at 1080p and 40 fps at 2K resolution, whereas the architecture presented in [23] is able to achieve 30 fps at 1080p video formats, using a similar amount of FPGA resources.

Considering the presented results, our architecture shows an efficient implementation of available resources in FPGA, overcoming the performance of previous state-of-the-art architectures.

| Search area          |       | 128x128 | 3      |       | 104x104 |       |       | 64x64 |       |

|----------------------|-------|---------|--------|-------|---------|-------|-------|-------|-------|

| Video sequences      | s1    | s2      | s3     | s1    | s2      | s3    | s1    | s2    | s3    |

| Encoding Time SW (s) | 13670 | 61602   | 135970 | 9392  | 42050   | 92863 | 4117  | 17881 | 39933 |

| % IME Time SW        | 95    | 96      | 95     | 90    | 94      | 93    | 83    | 86    | 85    |

| CTU/s SW             | 0.24  | 0.26    | 0.23   | 0.38  | 0.39    | 0.35  | 0.91  | 1.00  | 0.89  |

| CTU/s HW             | 14993 | 14993   | 14993  | 22625 | 22625   | 22625 | 59172 | 59172 | 59172 |

| HW gain              | 62260 | 57767   | 64800  | 59621 | 58312   | 65384 | 64856 | 59115 | 66477 |

**Table 2.8.** Time profile of the IME HEVC for a 64x64 CTU with video sequences *Race Horses*(s1), *Basketball Drive*(s2), and *People On Street*(s3)

Regarding the time profile of the HEVC IME module, a comparison between software and hardware executions has been performed. Tables 2.8 and 2.9 show the following information for different configurations allowed: The total time required to encode 10 frames of each video sequence with the software reference model, the percentage of the total time needed by the IME software module using a FS algorithm, the number of CTUs per second that can be computed by software and by hardware versions of the IME module, and finally, the gain obtained with the inclusion of our IME hardware module instead of the software one. These values depend on the size configurations,

| Search area          | 64x64 |       |       | 52x52  |        |        | 32x32  |        |        |

|----------------------|-------|-------|-------|--------|--------|--------|--------|--------|--------|

| Video sequences      | s1    | s2    | s3    | s1     | s2     | s3     | s1     | s2     | s3     |

| Encoding Time SW (s) | 3652  | 15892 | 35295 | 2634   | 11303  | 25293  | 1378   | 5748   | 12911  |

| % IME Time SW        | 85    | 87    | 86    | 79     | 81     | 81     | 60     | 63     | 62     |

| CTU/s SW             | 4     | 5     | 4     | 6      | 7      | 6      | 14     | 17     | 15     |

| CTU/s HW             | 76923 | 76923 | 76923 | 115607 | 115607 | 115607 | 297619 | 297619 | 297619 |

| HW gain              | 20383 | 17293 | 19457 | 20654  | 17384  | 19675  | 21096  | 17664  | 19912  |

**Table 2.9.** Time profile of the IME HEVC for a 32x32 CTU with video sequences *Race Horses*(s1), *Basketball Drive*(s2), and *People On Street*(s3)

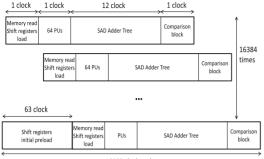

**Figure 2.5.** R/D performance for different CTU and search area sizes for the RaceHorses sequence

and in the case of the IME software module, also depend on the video sequence. Regarding these results, it could be conclude that the IME module is a bottleneck in the HEVC reference software, and if the IME software module is replaced by our FPGA-based device, the overall encoding time will be significantly reduced. In order to reduce the hardware complexity, allowing faster versions with reduced power consumption, the CTU size and the search area must be reduced as much as possible, without causing degradation in the encoding process, neither decreasing the overall video quality nor reducing the compression rate, as can be seen in Figure 2.5. In Figure 2.5, we show the video quality of the test video sequence RaceHorses (s1) for each CTU and

| CTU   | Full Diamond |            | Full       |

|-------|--------------|------------|------------|

| size  | search SW    | search SW  | search HW  |

| 64x64 | 4.11 s       | 4.65E-02 s | 6.67E-05 s |

| 32x32 | 2.48E-01 s   | 3.05E-03 s | 1.30E-05 s |

Table 2.10. Average CTU IME time with 2xCTU search area size

search area sizes at different compression levels (QP values). As can be seen, there are negligible differences in terms of R/D between the CTU size and search area size. Although R/D differences may depend on the video content, similar results were obtained for the other two video sequences tested.

The Diamond Search (DS) algorithm is used by default in the HM reference software due to this is about 90 times as fast as the FS algorithm in software, with the disadvantage that it does not guarantee finding optimal MVs, and as consequence video quality could be affected. Finally, as can be seen in Table 2.10, the inclusion of our IME hardware module, using FS algorithm, will speed up the IME computation of diamond-like search algorithm 230 times and 700 times for 32x32 and 64x64 CTU sizes, respectively. Therefore, as conclusion, the use of our IME hardware accelerator designed in a FPGA platforms are mandatory when real-time UHD video encoding is the objective.

#### 2.2.1.1 Prototype implementation

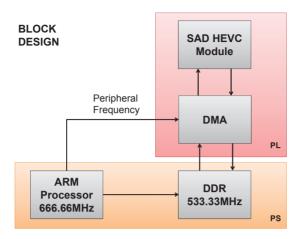

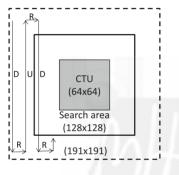

Following the same research line about video coding acceleration, the previous hardware HEVC IME design has been evaluated when applied to a SoC platform. In this case, the Xilinx SoC, Zynq-7 Mini-ITX Motherboard XC7Z100 (xc7z100ffg900-2) has been used, as hardware platform.

A SoC consist of two well-defined parts, a PS based on an ARM processor and several hard peripherals like Ethernet, USB, etc., and a PL been made up of a FPGA. In Figure 2.6 the top-level hardware architecture is showed, where an ARM processor manages the transfer between the IME SAD module and a Double Data Rate (DDR) memory which stores both reference and current frames, by a Direct Memory Access (DMA) module. With this hardware platform, ARM processor works at 666.66 MHz, and the DDR at 533.33 MHz, whereas the clock frequency of the PL is restricted by the maximum frequency of the SAD HEVC module which is the responsible for the IME calculation. In the case of 64x64 CTU size, the PL can work at 220 MHz

Figure 2.6. Top-level hardware architecture

**Figure 2.7.** Percentage of software reference encoding time required for SAD module with a FS strategy.

whereas with a 32x32 CTU size the PL clock frequency is fixed as maximum in the evaluation board used, 250 MHz.

In order to perform several experiments with the HEVC IME and to observe how the different parameters impact on the Rate Distortion (R/D) performance and coding complexity of the HEVC encoder, the same configurations and models than in the previous section have been choosen (for instance, CTU sizes of 64x64 and 32x32, and their corresponding Search Range (SR) sizes as 100%, 80%, and 50% of the CTU size, and HEVC HM 14 software reference model). In this approach, another two video sequences from the HEVC common conditions video set were selected: ParkScene at 1920x1080 resolution (24 fps) and Traffic 2560x1600 (30 fps).

(b) BD-Rate obtained with a 64x64 CTU size and several SR sizes

Figure 2.8. BD-Rate values with (a) 32x32, and (b) 64x64 CTU sizes

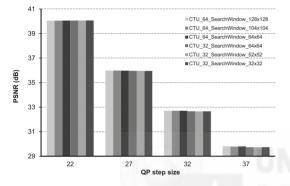

In Figure 2.7, the percentage of the overall encoding time that was spent by HEVC reference software using the FS algorithm is shown. Generally, the encoder spends more time in the IME module when both the CTU size and Search Range (SR) are higher, as expected. The time spent by HEVC encoder to perform the ME ranges between 63% to 95% of the time required to encode the whole video sequence.

In addition, the impact of the previous parameters on the R/D performance have been analyzed, using the Bjontegaard metric (BD-rate) [24] which allows to compute the average per cent of bitrate overhead/saving between two rate-distortion curves.

(b) CUs per second processed for a 64x64 CTU size

Figure 2.9. CUs per second processed for each DMA burst size with our proposed SAD HEVC module

In Figure 2.8, it can be observed the BD-rate obtained with different CTU and SR sizes for the two video sequences selected. In order to obtain the percentage of BD-Rate, each R/D curve with its corresponding configuration is compared with a reference R/D curve whose configuration corresponds to a 64x64 CTU size and a search range of  $\pm 64$  (128x128 search area size). As can be seen, there are slight differences between the SR sizes for a given CTU size, especially for a CTU size of 64x64 where the bitrate penalty is up to 0.1% (see Figure 2.8(b)). In the case of 32x32 CTU size, we obtain higher bitrate overheads, up to 2.7% (see Figure 2.8(a)).

Figure 2.10. Hardware Processing Time for different DMA burst sizes