# Sequential Switching Shunt Regulation Using DC Transformers for Solar Array Power Processing in High **Voltage Satellites**

CARLOS ORTS

AUSIÀS GARRIGÓS D, Senior Member, IEEE

DAVID MARROQUÍ <sup>D</sup>

Miguel Hernandez University of Elche, Elche, Spain

#### ANDREAS FRANKE

European Space Agency, Noordwijk, The Netherlands

This article proposes a solar array regulation technique for a high-voltage satellite power bus. The regulation method combines ON-OFF control at low frequency, i.e., kHz range, of highly efficient isolated and unregulated dc-dc converters operating at high frequency, i.e., hundreds of kHz. Although this technique can adopt different implementations, this article deals with a hysteretic voltage control loop at low frequency, also known sequential switching shunt regulator (S3R), and unregulated, isolated, current-fed, zero-voltage, and zero-current push-pull dc-dc converters. Design guidelines and experimental validation are provided.

Manuscript received 3 July 2023; revised 19 September 2023; accepted 9 October 2023. Date of publication 17 October 2023; date of current version 9 February 2024.

DOI. No. 10.1109/TAES.2023.3325314

Refereeing of this contribution was handled by R. Meyer.

This work was supported by the European Space Agency under Grant 4000136441/21/NL/GLC/my.

Authors' addresses: Carlos Orts, Ausiàs Garrigós, and David Marroquí are with the Industrial Electronics Group, Miguel Hernandez University of Elche, 03202 Elche, Spain, E-mail: (corts@umh.es; augarsir@umh.es; dmarroqui@umh.es); Andreas Franke is with the Power Management and Distribution Section, Power Systems, EMC & Space Environments Division, Electrical Department, European Space Agency, 2201 Noordwijk, The Netherlands, E-mail: (andreas.franke@esa.int). (Corresponding author: Carlos Orts.)

#### **NOMENCLATURE**

Acronyms

**BCR** Battery charge regulator.

**BCDR** Battery charge discharge regulator.

**BDR** Battery discharge regulator.

DC Direct current.

DC-DC Direct current to direct current. DCX Direct current transformer. DET Direct energy transfer.

**ECSS** European Cooperation for Space Standardiza-

**EMI** Electromagnetic interference.

EP Electrical propulsion.

**EPC** Electronic power conditioner.

**GEO** Geostationary orbit. HV High voltage. **LEO** Low Earth orbit. LV Low voltage. **MEA** Main error amplifier.

**MPP** Maximum power point.

**MPPT** Maximum power point tracking. **PCU** Power conditioning unit. **PPU** Power processing unit. SAS Solar array section.

S3DCX Sequential switching shunt DCX regulator.

S<sub>3</sub>R Sequential switching shunt regulator.

Switching shunt regulator. SSR Travelling wave tube amplifier. **TWTA**

**ZCS** Zero current switching. **ZVZC** Zero voltage zero current. **ZVS** Zero voltage switching.

#### I. INTRODUCTION

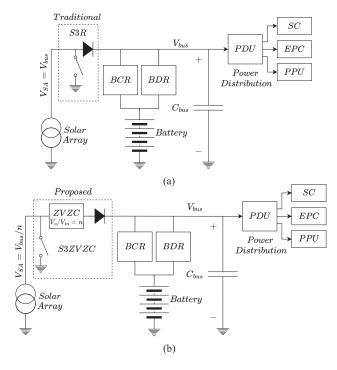

Solar array regulation is a critical power conversion function for any spacecraft. Two main methods are dominant nowadays: MPPT dc-dc converters and SSRs. While the first approach is typical in low- and medium-power LEO and interplanetary missions using unregulated bus architectures, the second method is widely used in medium and high-power satellites for GEO satellites using fully regulated bus architectures, being the S3R [1], [2], [3], [4], the most common SSR employed. The fully regulated bus is realized by the PCU, which integrates the SSR, the BCR, and the BDR, as represented in Fig. 1(a) [5], [6]. In the European Space standard [7], 100–120 V dc bus voltage is recommended for power levels higher than 8 kW, hence, most of the space companies have adapted their products to this voltage for the largest platforms. However, 100 V starts to be inadequate for the actual needs, since the most powerful platforms already reach 20–25 kW, also motivated by the use of high-power EP systems [8]. Large bus current lead to high mass harness and considerable dc losses, but also impacts on the maximum bus impedance  $(Z_{\rm bus})$  and bus capacitor  $(C_{\text{bus}})$  [7]. Furthermore, EP systems require high-power, high-voltage supplies, which are provided by the PPUs directly connected to the regulated bus. Two-level

<sup>© 2023</sup> The Authors. This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

Fig. 1. High-power spacecraft electrical architecture. (a) Traditional [5]. (b) Proposed approach.

power conversion results in a penalty on efficiency and with obvious consequences on the thermal design, size, and mass. Besides, other systems, such as EPCs for TWTAs, also demand high-voltage supplies and could benefit of high voltage bus.

As a result, a higher bus voltage, around 300 V, is being considered, and two main approaches have been pondered to address its implementation. In [9], the solar array voltage is increased up to 300–350 V, and a DET connection from the solar generator to the electric thruster is suggested. The BCDR controls the bus voltage. While it is a conceptually simple solution, there are relevant technical challenges associated with the high-voltage solar array, such as arcing due to differential charging of the different materials, high-voltage slip rings, qualification, and cost [9]. Furthermore, it is a costly solution that requires full requalification of the solar array if the bus voltage is changed. In [10], a two-stage approach is proposed for an ion-thruster supply with MPPT tracking. The main advantages of this approach are the simplicity and heritage, since only well-known power regulators are used for its implementation. Besides, it exhibits very good regulation for large power transients that happen in ion-thrusters. The main disadvantage is the efficiency penalty due to S3R diodes and the Weinberg converter losses.

In [11], a two-bus approach is presented, implementing a high-voltage bus (HV $_{\rm bus}$ ) at 450 V, and low-voltage bus (LV $_{\rm bus}$ ) at 100 V, featuring an integrated power processing dc–dc converter. The power cell can operate in different operating modes, including MPPT and bus regulated for both busses, HV $_{\rm bus}$  and LV $_{\rm bus}$ . However, it requires a complex power processing dc–dc converter and control, making

the practical implementation difficult with space-qualified electronic parts.

In this work, as presented in Fig. 1(b), a different approach for the solar array regulator is proposed. It uses highly efficient, isolated, unregulated, constant gain, high-frequency dc–dc converter, also known as "DC-Transformer" (DCX). The DCXs, switching at hundreds of kHz or more, are controlled as traditional S3R power cells at low frequency, i.e., kHz range, [1], [12]. This concept is adaptable to any regulated or unregulated bus. The design of BCRs and high-power BDRs [13], [14] are topics already discussed in the literature, therefore, these will not be covered in this work.

Different DCX topologies have been proposed for industrial, medical, telecommunications, and many other areas. Resonant techniques [15], and particularly the *LLC* converter [16], [17], have been widely accepted, but these are mostly oriented to have regulated outputs with complex control loops. Another type of unregulated DCX with ZVS and ZCS are described in [18] and [19]. Both converters use the magnetizing current of the transformer to achieve ZVS for all switches, but the method to achieve ZCS is slightly different. In [18], the leakage inductance of the transformer resonates with the output capacitor to achieve ZCS without any inductor. In [19], the converter is current-fed and the resonant circuit is formed by the leakage inductance and a resonant capacitor placed at the input. A fundamental feature of these DCXs is that the conversion gain is just the transformer turns ratio, so they are very simple and robust to parameter drifts. A detailed analysis of those types of DCX can be found in [20]. In the case at hand, the method proposed in [19] is better suited than the one described in [18], because a photovoltaic source inherently behaves as a current source below its MPP. This is also reinforced by the fact that the solar array harness inductance is relatively large in high-power satellites. Besides, a large capacitor is required as the main bus capacitor at the secondary side to fulfill the output impedance requirements [7]. As discussed in [20], any dual-ended topology is suitable, but current-fed ZVZC push-pull is widely used in satellite applications, mainly in EPC for TWTA [19].

In summary, the proposed S3DCX has the following benefits when compared to the existing solutions.

- It is a simple concept that can be implemented with different DCX topologies, allowing voltage decoupling between solar array and distribution bus, which overcomes the limitations of the direct energy transfer regulators and provides increased flexibility in solar array design.

- 2) Higher (or lower) bus voltage could be achieved with very high efficiency (>95%) end to end.

- It can be used as direct replacement of the S3R with minimum changes in regulated or unregulated bus architectures and variations.

- 4) It is highly modular and accepts parallel and series connection of isolated secondary sides to achieve higher current and voltage.

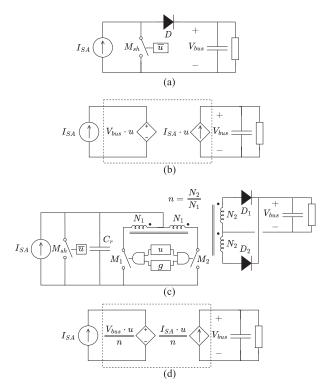

Fig. 2. DET shunt regulator. (a) Simplified schematic. (b) Large signal averaged model. DCX (current-fed ZVZC push-pull). (c) Power cell schematic. (d) Averaged model.

The rest of this article is organized as follows. Section II introduces the S3DCX power cell as well as a particular implementation and modeling of the regulator. Section III details the design and simulation of the S3DCX for a 300 V–2 kW prototype. Section IV details the experimental validation of the proposed prototype and discusses the results. Finally, Section V concludes this article.

#### II. S3DCX: POWER CELL AND REGULATOR

The current-fed ZVZC push—pull, represented in Fig. 2(c), is considered as DCX for this work. Briefly, the main benefits of the selected topology are as follows.

- Galvanic isolation provides easy adjustment of required output by transformer turns ratio and possibility of secondary side output connections (series and parallel).

- It takes advantage of the natural solar array behavior and harness inductance to have a nearly constant current source.

- 3) It uses for its advantage all the parasitic elements of the transformer in a resonant manner, resulting in a very compact, simple, lightweight, and high efficiency solution.

- 4) All power semiconductors are operated in ZVS and ZCS.

- 5) ZVS and ZCS (neglecting magnetizing current) are load independent in a wide range.

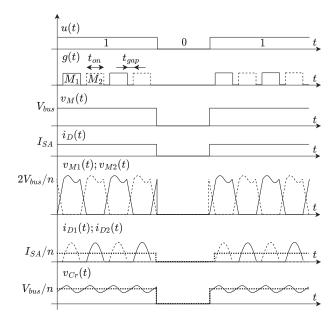

Fig. 3. DET and DCX main waveforms sketch.

- Simple and low loss gate drive (rad-hard driver implementation is not linked to any complex driver integrated circuit).

- 7) Good power semiconductor utilization (>75% equivalent duty cycle).

- 8) Operation at fixed frequency and duty cycle (very simple and robust drive pulse generation).

- 9) Reduced number of components.

- 10) Very low EMI.

Fig. 2(a) and (b) represents the schematic and the large signal averaged model for the DET shunt regulator, respectively, and Fig. 2(c) and (d) shows the circuit schematic and averaged model of the proposed DCX. The control signal, u, dictates the power transfer from the solar array to the main bus in both cases (1), but the working principle is slightly different. When u = 1, in the DET case, the transistor  $M_{\rm sh}$  is OFF and the diode D connects the solar array section to the bus, while in the DCX, the M<sub>1</sub> and M<sub>2</sub> driving pulses, g, operating at switching frequency,  $f_s$ , enable the power transfer. When u = 0, the transistor  $M_{\rm sh}$  shunts the solar array in the DET and the DCX power cells. An important difference is that DCX allows voltage and current conversion ratio (gain is transformer turns ratio, n) when it transfers power to the bus, as it can be noted in the DCX averaged model. The main waveforms of the power cells are represented in Fig. 3, being from top to bottom: shunt driving signal, u; DCX driving signal, g;  $M_{\rm sh}$  drain-source voltage of DET shunt regulator,  $v_M$ ; diode current of DET shunt regulator,  $i_D$ ;  $M_1$  and  $M_2$  drain-source voltage of DCX,  $v_{M1}$ ,  $v_{M2}$ ; rectifier diode current of DCX,  $i_{D1}$ ,  $i_{D2}$ , and resonant capacitor voltage of DCX,  $v_{Cr}$ .  $M_1$  and  $M_2$ can be also used to perform power control transfer, u, and therefore one transistor is saved, however,  $M_{\rm sh}$  simplifies

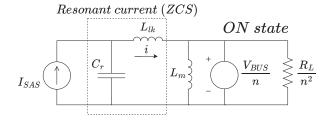

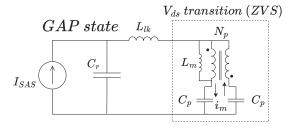

Fig. 4. DCX equivalent circuits for ON and GAP states.

current limiting during shunt operation

$$u(t) = \begin{cases} 1 : SA & \text{power transfer} \\ 0 : SA & \text{shunted.} \end{cases}$$

(1)

The working principle of the DCX can be explained with the two equivalent circuits shown in Fig. 4. During the ON state, i.e.,  $M_1$  or  $M_2$  is in conduction, a resonant switch current occurs due to the resonant circuit formed by the resonant capacitor,  $C_r$ , and the transformer leakage inductance,  $L_{lk}$ . During the GAP state, i.e.,  $M_1$  and  $M_2$  are turned-OFF, the magnetizing current charges and discharges all the parasitic capacitances, i.e., MOSFETS, diodes, and transformer.

The analysis of the ON state circuit results in the resonant current, i, whose governing differential equation is given by (2). MOSFET current is  $i_M = i - i_m$ , being  $i_m$ , the magnetizing current and diode current is  $i_D = i_M/n$

$$L_{lk}C_r \frac{\partial^2 i}{\partial t^2} + i = I_{SA}. \tag{2}$$

On the other hand, the analysis of the GAP state results in the governing differential (3), where the resonant circuit is formed by the magnetizing inductance,  $L_m$ , and the parasitic capacitance,  $C_p$ , given by (4).  $C_M$  is the parasitic MOSFET capacitance,  $C_{\mathrm{TR}}$  is the parasitic transformer capacitance and  $C_D$  is the diode capacitance referred to the primary side

$$L_m C_p \frac{\partial^2 i_m}{\partial t^2} + \frac{i_m}{2} = 0 \tag{3}$$

$$C_p = C_M + C_{TR} + C_D \cdot n^2. \tag{4}$$

The detailed design procedure to solve (2) and (3) for ZVS and ZCS conditions can be found in the Appendix. It is clear from the ON state equivalent circuit that  $\langle V_{Cr} \rangle =$  $V_{\rm bus}/n$ , implying that the solar array operating point, and therefore, the power injected to the bus, can be controlled by the bus voltage in closed-loop operation.

Satellite solar arrays are typically divided into several sections, i.e., an arrangement of several solar cell strings in

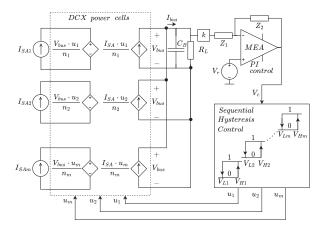

S3DCX: Sequential hysteresis control scheme.

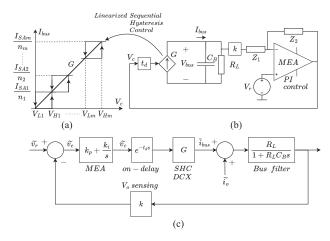

Fig. 6. S3DCX. (a) Linearized sequential hysteresis control. (b) Small-signal linear model. (c) Voltage feedback loop.

parallel. In the proposed regulator, each section is attached to one DCX, refer to Fig. 2(c). In a sequential control scheme, some DCX converters are permanently ON providing power to the bus, while others DCX are OFF and only one DCX is turning ON and OFF to eventually perform output voltage regulation. This can be achieved by sequential hysteretic control [1], as illustrated in Fig. 5, being this scheme one of the most common methods employed in solar array regulation for medium and large satellites.

The linearized model of the S3DCX regulator is given by (5), resulting in a voltage-controlled current-source that supplies the main bus capacitor, represented in Fig. 6. The voltage loop gain,  $T_v(s)$  and the closed-loop output impedance  $Z_O(s)$  are given by (6) and (7), respectively

$$G = \frac{I_{\text{bus}}}{V_C} = \frac{\sum_{i=1}^{n} I_{SA_i}/n_i}{V_{Hm} - V_{L1}}$$

(5)

$$T_{v}(s) = kG \frac{k_{p}(s + k_{i}/k_{p})}{s} \frac{1}{C_{B}(s + (1/R_{L}C_{B}))}$$

(6)

$$Z_{O}(s) = \frac{\tilde{v}_{o}}{\tilde{i}_{o}} = \frac{1}{C_{B}(s + (1/R_{L}C_{B}))[I + T_{v}(s)]}.$$

(7)

$$Z_{O}(s) = \frac{v_{o}}{\tilde{i}_{o}} = \frac{1}{C_{B}(s + (1/R_{L}C_{B}))[I + T_{v}(s)]}.$$

(7)

To avoid phase and gain margin degradation, [21], the regulator turn-ON delay,  $t_d$ , must be smaller than  $1/\omega_c$ , being

TABLE I S3DCX: Main Design Parameters

| Description                                                                                                                        | Value                 | Comment                                      |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------|--|--|--|--|

| Solar array section (SAS) – Agilent E4351B simulator                                                                               |                       |                                              |  |  |  |  |

| V <sub>OC</sub>                                                                                                                    | 120V                  | Open-circuit voltage                         |  |  |  |  |

| $V_{MP}$ 110V                                                                                                                      |                       | Maximum power voltage                        |  |  |  |  |

| I <sub>SC</sub> 4A                                                                                                                 |                       | Short-circuit current                        |  |  |  |  |

| I <sub>MP</sub> 3.9A                                                                                                               |                       | Maximum power current                        |  |  |  |  |

| $P_{MP}$                                                                                                                           | 429W                  | Maximum power                                |  |  |  |  |

| $C_{SAS}$                                                                                                                          | 200nF                 | Agilent E4351B                               |  |  |  |  |

| $L_h$                                                                                                                              | 33μΗ                  | Added inductance                             |  |  |  |  |

| DCX transformer – push-pull (N <sub>1</sub> =N <sub>1a</sub> =N <sub>1b</sub> ; N <sub>2</sub> =N <sub>2a</sub> =N <sub>2b</sub> ) |                       |                                              |  |  |  |  |

| Core                                                                                                                               | RM14                  | Material 3C95                                |  |  |  |  |

| $n=N_2/N_1$                                                                                                                        | 15/5                  | V <sub>SAS</sub> =100V; V <sub>O</sub> =300V |  |  |  |  |

| DCX & shunt – circuit                                                                                                              |                       |                                              |  |  |  |  |

| $C_{\rm r}$                                                                                                                        | 0.5 μF                | CB182G0105J                                  |  |  |  |  |

| M <sub>1</sub> ; M <sub>2</sub> ;                                                                                                  | IXTQ42N25P            | Si MOSFET (250V, 42A)                        |  |  |  |  |

| $M_{sh}$                                                                                                                           |                       | SI MOSFET (230V, 42A)                        |  |  |  |  |

| $D_1; D_2$                                                                                                                         | STPSC10H12            | SiC diode (1.2kV, 10A)                       |  |  |  |  |

| $t_{on}$                                                                                                                           | 2.8µs                 | f <sub>s</sub> =135kHz; D=0.378              |  |  |  |  |

| $t_{\mathrm{gap}}$                                                                                                                 | 0.9μs                 | f <sub>output</sub> =270kHz                  |  |  |  |  |

| R <sub>cl</sub>                                                                                                                    | $50 \mathrm{m}\Omega$ | Max shunt current= 14A                       |  |  |  |  |

| Control loop                                                                                                                       |                       |                                              |  |  |  |  |

| k                                                                                                                                  | 4.08·10 <sup>-3</sup> | ADUM3190, V <sub>ref</sub> =1.225V           |  |  |  |  |

| k <sub>p</sub>                                                                                                                     | 298.8                 | Split into three stages                      |  |  |  |  |

| k <sub>i</sub>                                                                                                                     | $97.96 \cdot 10^3$    |                                              |  |  |  |  |

| t <sub>d</sub>                                                                                                                     | < 25µs                |                                              |  |  |  |  |

| G                                                                                                                                  | 1.11                  |                                              |  |  |  |  |

| $R_{\rm L}$                                                                                                                        | > 45Ω                 | $P_{Omax}=2kW; V_O=300V$                     |  |  |  |  |

| $C_{BUS}$                                                                                                                          | 400μF                 | B32778G1206K000                              |  |  |  |  |

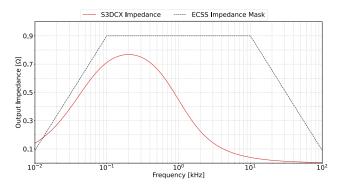

$\omega_c$  the crossover frequency of the loop gain (6),  $|T_v(j\omega_c)| = 1$ . The closed-loop output impedance is constrained by the output impedance mask, defined in the standard [7], clause 5.7.2.0.

## III. DESIGN, SIMULATION, AND PROTOTYPE IMPLE-MENTATION

A 2 kW, five power-cell S3DCX regulator has been designed, simulated, and implemented. Detailed step-by-step calculations are included in the Appendix.

## A. Design

The main characteristics of the S3DCX regulator and the solar array simulator are summarized in Table I.

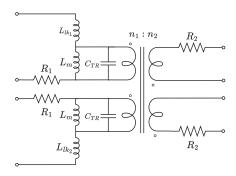

Based on the simplified transformer circuit model shown in Fig. 7, measured parameters for the five transformers are included in Table II. These parameters are, magnetizing inductance  $L_m$ , leakage inductance  $L_{lk}$ , parasitic capacitance of the transformer  $C_{\rm TR}$ , resistance of the primary  $R_1$  and secondary winding  $R_2$ , and resonant frequency  $f_{\rm res}$ .

Fig. 7. S3DCX: Transformer equivalent circuit model.

TABLE II S3DCX: Transformer Characterization

| $L_{m}$ | $L_{lk1}$ | $L_{lk2}$ | $C_{TR}$ | $R_1$       | $R_2$       | $f_{res}$ |

|---------|-----------|-----------|----------|-------------|-------------|-----------|

| [µH]    | [nH]      | [nH]      | [pF]     | $[m\Omega]$ | $[m\Omega]$ | [kHz]     |

| 172.8   | 650       | 680       | 235      | 9.7         | 41.6        | 789       |

| 174.5   | 680       | 610       | 211      | 9.1         | 40.9        | 830       |

| 169.7   | 765       | 690       | 174      | 9.3         | 41.6        | 925       |

| 168.9   | 590       | 625       | 162      | 11.8        | 41.2        | 962       |

| 165.1   | 590       | 630       | 201      | 13.1        | 41.9        | 874       |

Fig. 8. S3DCX output impedance and ECSS impedance mask [7].

## B. Simulation: Switching and Large-Signal Averaged Models

Computer simulation models have been implemented for both, switching and large-signal averaged versions. The output impedance of the S3DCX, which meets the impedance mask required by the European space standard [7], clause 5.7.2.o., is represented in Fig. 8.

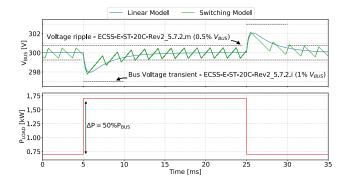

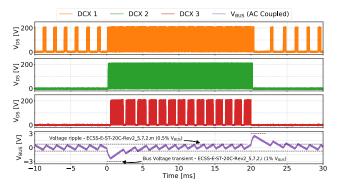

A half bus power load step simulation is shown in Fig. 9. Nominal bus voltage ripple and bus voltage transient meet the European space standard [7], clauses 5.7.2.m and 5.7.2.i.1, respectively.

The S3DCX prototype is shown in Fig. 10. The five DCXs are identical, and the output connections are hardwired to allow independent or series connections to the output bus capacitor, which is external and not shown in the figure. The MEA is implemented using an isolated error amplifier, and  $t_{\rm on}$  and  $t_{\rm gap}$  signals are obtained using only discrete electronic parts.

Fig. 9. S3DCX transient response simulation results. Top figure: Output voltage (switching and large-signal averaged models). Bottom figure: power load step.

Fig. 10. S3DCX prototype: 2 kW, five power cells.

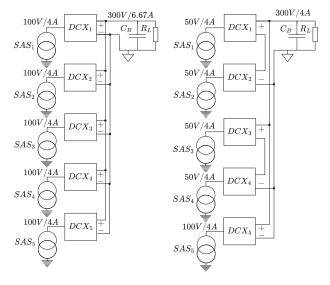

Fig. 11. Left figure: S3DCX five-independent output configuration. Right figure: Two solar array sections with two DCX in series and one independent.

#### IV. EXPERIMENTAL VALIDATION

Several tests have been carried out to validate the proposed solar regulation concept using independent and series configurations at the output of the regulator, as represented in Fig. 11.

#### A. DCX: Shunt and ZVZC Operation

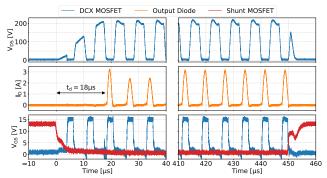

Fig. 12 shows the detail of the ON (u = 1) and OFF (u = 0) of the DCX. It is clearly observed from the MOSFET

Fig. 12. Left: DCX ON detail. Right: DCX OFF detail. Top:  $V_{\rm DS}$   $M_1$ , Middle: I  $D_1$ , Bottom: Blue trace:  $V_{\rm GS}$   $M_1$ , and Red trace:  $V_{\rm GS}$  shunt transistor.

TABLE III DCX: Efficiency Measurements

| $I_{SAS}$ | DCX1 | DCX2 | DCX3 | DCX4 | DCX5 |

|-----------|------|------|------|------|------|

| [A]       | [%]  | [%]  | [%]  | [%]  | [%]  |

| 1         | 92.5 | 92.5 | 92.0 | 91.9 | 92.0 |

| 2         | 95.3 | 95.2 | 94.8 | 94.8 | 94.8 |

| 3         | 95.9 | 95.3 | 95.5 | 95.4 | 95.5 |

| 4         | 95.8 | 95.8 | 95.4 | 95.1 | 95.3 |

Fig. 13. S3DCX voltage regulation. Top: DCX 1:  $V_{\rm DS}$  M<sub>1</sub>; Middle-top: DCX 2:  $V_{\rm DS}$  M<sub>1</sub>; Middle-bottom: DCX 3:  $V_{\rm DS}$  M<sub>1</sub>; Bottom: bus voltage (ac coupled).

voltage and diode current that ZVS and ZCS are achieved even during the transients. Besides, ON-delay,  $t_d$ , is limited to 18  $\mu$ s. It can be also noticed that the shunt transistor goes into current limitation mode during the OFF action to discharge the parasitic capacitance of the solar array and the resonant capacitor of the DCX.

## B. DCX: Efficiency

The efficiency of each DCX has been measured at different solar array currents, which could represent different irradiance levels or different solar array orientation, refer to Table III. Efficiency measurements also include power consumption of ancillary electronics and is close to 95.5% in nominal operation.

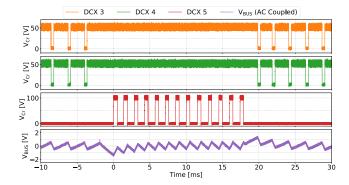

Fig. 14. S3DCX voltage regulation—output series connection. Top: DCX 3:  $V_{Cr}$ ; Middle Top: DCX 4:  $V_{Cr}$ ; Middle Bottom: DCX 5:  $V_{Cr}$ ; Bottom: bus voltage (ac coupled).

## C. S3DCX: Voltage Regulation

Fig. 13 illustrates the regulator's response under a 1 kW load power step, from 100 W to 1.1 kW (50% of the bus power). The configuration of the S3DCX is the one indicated in Fig. 11(left). At the beginning, DCX 1 is regulating the output voltage and the rest of DCX are fully OFF. Once the load step happens, DCX 1 and DCX 2 go to fully ON and DCX 3 regulates the output voltage. As it can be observed in the ac bus voltage waveform (bottom), the steady-state bus voltage ripple does not exceed the 0.5% of the nominal bus voltage (1.5 V) and the peak values during load transients are within 1% of the bus voltage (3 V). Bus voltage steady state is reached in less than 5 ms.

# S3DCX: Output Series Connection—Voltage Regulation

Fig. 14 illustrates the operation of the regulator with the configuration represented in Fig. 11(right) under a step load of approximately 500 W. At the beginning, DCX 3 and DCX 4 are regulating the bus voltage and the load step forces the operation of DCX 5. It is important to note that DCX 3 and DCX 4 are accommodating 50 V solar sections and, DCX 5 at 100 V solar section, as it can be observed from the voltage measured in the resonant capacitor,  $C_r$ , of each DCX.

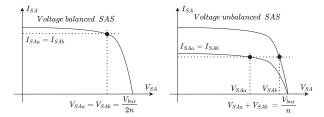

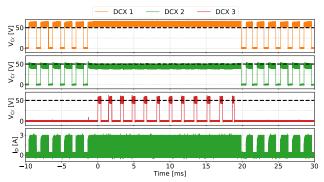

# E. S3DCX: Output Series Connection—Unbalanced Solar Array Currents

The last results show the proper operation of the regulator with output series connection and unbalanced solar array currents. The regulator has been configured as represented in Fig. 11(right), but SAS 2 reduces its current to  $I_{\rm SC}=3.2$  A and  $I_{\rm MP}=3$  A. As depicted in Fig. 15, as the output current is limited, the operating point of the solar sections adjust to a value where both currents are equal. This effect is clearly shown in Fig. 16, where SAS 1 and SAS 2 exhibit different voltages, either during regulation or fully ON operation modes. It is also worth to note, that SAS 3 operates at the nominal value, since SAS 3 and SAS 4 are not unbalanced. Thus, it is important to remark that DCX

Fig. 15. Sketch of balanced and unbalanced solar array sections in output series connection.

Fig. 16. S3DCX voltage regulation – output series connection and unbalanced solar array currents. Top: DCX 1:  $V_{Cr}$ ; Middle Top: DCX 2:  $V_{Cr}$ ; Middle Bottom: DCX 3:  $V_{Cr}$ ; Bottom: DCX 1: I  $D_1$ .

output series connection is possible, with no loss of ZVZC conditions, even with unequal I-V curves of the solar array.

#### V. CONCLUSION

This article introduces a different concept for solar array regulation that solves some of the problems associated to direct energy transfer regulators commonly used in bus regulated satellites. The use of the proposed DCX topology provides two degrees of freedom for regulating bus voltage: transformer turns ratio, and output series connection of individual solar array sections, offering true adaptability to accommodate different types of solar arrays. Although this concept has been validated for a high voltage bus at 300 V, assuming step-up voltage conversion, other approaches are possible. Design example, computer simulation, and experimental prototype has been also included in this article to show the operating principles of the proposed regulator. Next steps include higher bus voltage (600 and 900 V), miniaturization of DCX increasing switching frequency (GaN power semiconductors and planar magnetics) and digital implementation (control and pulsewidth modulated gate signals).

#### **APPENDIX**

## A. Design Guidelines: ZVZC Converter

1) Estimate the parasitic capacitance,  $C_p$  (2), from power semiconductors and transformer

$$C_M \approx 500 \, \mathrm{pF}$$

$C_{TR} \approx 300 \, \mathrm{pF}$

$C_D \approx 100 \, \mathrm{pF}$

$$C_p = C_M + C_{TR} + C_D \cdot n^2 \approx 1.7 \text{ nF.}$$

(A-1)

2) Definition of the magnetizing current,  $i_m$ , as a percentage of the input current. An initial tentative of 20% of input current is considered. Low values  $i_m$  means larger transformers and longer  $t_{\rm gap}$ , but lower transformer losses and better ZCS transitions

$$i_m = 0.2I_{SA} = 0.8 \text{ A}.$$

(A-2)

3) Estimation of required gap time to charge the parasitic capacitance,  $t_{\rm gap}$ , and estimation of ON time,  $t_{\rm on}$ , as a percentage of  $t_{\rm gap}$  to maximize power transfer. Estimation of switching frequency,  $f_s$

$$t_{\text{gap}_{\text{min}}} > \frac{4V_{\text{bus}}C_p}{i_m n} = 0.85 \ \mu \text{s}$$

(A-3)

$$t_{on} \approx \frac{t_{\text{gap}_{\text{min}}}}{0.3} = 2.85 \,\mu\text{s} \tag{A-4}$$

$$f_s = \frac{1}{2(t_{\text{on}} + t_{\text{gap}})} = 135 \text{ kHz.}$$

(A-5)

4) Estimation of magnetizing inductance,  $L_m$  and transformer design

$$L_m = \frac{V_{\text{bus}}t_{\text{on}}}{2i_m n} = 178 \ \mu\text{H}.$$

(A-6)

5) Transformer design. From the above inputs, a RM14/I core and 3C95 material with five turns ON primary,  $n_1 = 5$ , and 15 turns ON secondary,  $n_2 = 15$  is considered. Measured values of five transformers will result in the following values (average of five measured transformers):

$$L_M \approx 170 \ \mu \text{H}$$

$C_{TR} \approx 200 \ \text{pF}$   $L_{lk} \approx 650 \ \text{nH}.$  (A-7)

- 6) Check if the transformer values are consistent with the original design and go back to step 1, if necessary.

- 7) Gap time,  $t_{gap}$ , calculation from measured values and using the following expressions:

$$t_{\text{gap}} = \frac{1}{\omega_{\text{gap}}}$$

$$\left(\arcsin\left[\frac{8L_m\cos(\theta)C_p\omega_{\text{gap}}}{t_{\text{on}}} + \sin(\theta)\right] - \theta\right) = 0.9 \ \mu\text{s}$$

$$\omega_{\text{gap}} = \frac{1}{\sqrt{L_MC_p}}$$

$$\tan(\theta) = \frac{-2}{\omega_{\text{gap}}t_{\text{on}}}.$$

(A-8)

8) Calculation of resonant frequency,  $\omega_r$ , to satisfy zero current switching condition. Resonant frequency is found by numerical methods

$$\cos(\omega_r t_{\rm on}) - \omega_r \frac{t_{\rm gap}}{2} \sin(\omega_r t_{\rm on}) = 1$$

$$f_r = \frac{\omega_r}{2\pi} \approx 300 \text{ kHz.} \tag{A-9}$$

9) Calculation of resonant capacitor,  $C_r$

$$C_r = \frac{1}{\omega_r^2 L_{lk}} \approx 500 \, n\text{F.} \tag{A-10}$$

Design Guidelines: S3ZVZC MEA

Definition of maximum bus voltage ripple as per ECSS-E-ST-20C Rev.2, clause 5.7.2.m

$$\Delta V_{\rm bus|\it pp} < 0.5\% V_{\rm bus}$$

$$\Delta V_{\rm bus|\it pp} = 1 \ \rm V. \equation (A-11)$$

11) Definition of bus capacitance as per ECSS-E-ST-20C Rev.2, clauses 5.7.2.m and 5.7.2.o

$$C_{\text{bus}} = 400 \ \mu\text{F}.$$

(A-12)

12) Definition of MEA voltage reference,  $V_{\rm ref}$ , and voltage feedback gain, K.  $V_{\rm ref}$  is given by the internal voltage reference of the isolated error amplifier

$$V_{\rm ref} = 1.225 \,\mathrm{V}$$

(A-13)

$$K = V_{\text{ref}} / V_{\text{bus}} = 4.083 \cdot 10^{-3}.$$

(A-14)

13) Definition of the hysteresis of the comparator and the transconductance of the regulator, G. Hysteresis voltage is selected as a function of the voltage supply rail and number of power cells. If the upper limit of the k cell is equal to the lower limit of the k+1 cell, and the transformer turns ratio of all power cells are the same, n, the transconductance of regulator is simply the transconductance of one power cell

$$V_{Hi} - V_{Li} = V_{HL} = 1.2 \text{ V}$$

(A-15)

$$G = I_{SA} / (n \cdot V_{HL}) = 1.11 \text{ A/V}.$$

(A-16)

14) Calculation of proportional gain and integral term of the MEA,  $k_p$  and  $k_i$ , respectively,  $k_i$  is adjusted to be one decade below the crossover frequency of the voltage loop

$$k_p = \frac{V_{HL}}{K\Delta V_{\text{bus}|pp}} = 293.88$$

(A-17)

$$k_i = k_p \frac{\omega_c}{10} = \frac{k_p^2 KG}{10C_{\text{bus}}} = 97.96 \cdot 10^3 \text{s}^{-1}.$$

(A-18)

## REFERENCES

- D. O'Sullivan and A. H. Weinberg, "The sequential switching shunt regulator (S3R)," in *Proc. 3rd ESTEC Spacecraft Power Condition*ing Seminar, 1977, pp. 123–131.

- [2] Y. Meng, D. Zhang, and H. Zhu, "Negative effects of unexpected energy on sequential switching shunt regulator and suppression methods for high-power satellite," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 58, no. 3, pp. 2281–2290, Jun. 2022.

- [3] H. Zhu and D. Zhang, "Design considerations of sequential switching shunt regulator for high-power applications," *IEEE Trans. Ind. Electron.*, vol. 67, no. 11, pp. 9358–9369, Nov. 2020.

- [4] X. Jin, H. Lin, W. Yao, and Z. Lu, "Sequential switching shunt regulator with improved controller to suppress the influence of doublesection phenomenon," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 10, no. 5, pp. 5318–5331, May 2022.

- [5] A. Capel, D. O'Sullivan, and J. C. Marpinard, "High-power conditioning for space applications," *Proc. IEEE*, vol. 76, no. 4, pp. 391–408, Apr. 1988.

- [6] A. Capel and P. Perol, "Comparative performance evaluation between the S4R and the S3R regulated bus topologies," in *Proc. IEEE 32nd Annu. Power Electron. Spec. Conf.*, 1963, pp. 1963–1969, doi: 10.1109/PESC.2001.954409.

- [7] Space Engineering Electrical and Electronic, ECSS-E-ST-20C Rev.2, Apr. 2022.

- [8] C. G. Zimmerman et al., "Development and qualification of the eurostar neo solar array," in *Proc. Eur. Space Power Conf.*, 2019, pp. 1–5.

- [9] J. B. de Boissieu et al., "High voltage electrical power system architecture optimized for electrical propulsion and high-power payload," in *Proc. Eur. Space Power Conf.*, 2019, pp. 1–6.

- [10] J. M. Blanes et al., "Two-stage MPPT power regulator for satellite electrical propulsion system," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 47, no. 3, pp. 1617–1630, Jul. 2011.

- [11] M. Fu, D. Zhang, and T. Li, "New electrical power supply system for all-electric propulsion spacecraft," *IEEE Trans. Aerosp. Electron.* Syst., vol. 53, no. 5, pp. 2157–2166, Oct. 2017.

- [12] A. Garrigos, J. A. Carrasco, J. M. Blanes, and E. Sanchis, "Modeling the sequential switching shunt series regulator," *IEEE Power Electron. Lett.*, vol. 3, no. 1, pp. 7–13, Mar. 2005.

- [13] J. B. Ejea et al., "Optimized topology for high efficiency battery discharge regulator," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 44, no. 4, pp. 1511–1521, Oct. 2008.

- [14] E. Sanchis et al., "Bidirectional high-efficiency nonisolated step-up battery regulator," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 47, no. 3, pp. 2230–2239, Jul. 2011.

- [15] R. P. Severns, "Topologies for three-element resonant converters," IEEE Trans. Power Electron., vol. 7, no. 1, pp. 89–98, Jan. 1992.

- [16] T. Kim, S.-H. Choi, D. Choi, J.-E. Park, and G.-W. Moon, "Double fault-tolerant LLC resonant converter with reconfiguration method," *IEEE Trans. Ind. Electron.*, vol. 70, no. 5, pp. 4651–4661, May 2023.

- [17] L. Wang, D. Zhang, Y. Yang, and H. Li, "Two-stage factorized power architecture DC-DC converter for spacecraft secondary power supply system," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 10, no. 5, pp. 5392–5413, May 2022.

- [18] Y. Ren, M. Xu, J. Sun, and F. C. Lee, "A family of high power density unregulated bus converters," *IEEE Trans. Power Electron.*, vol. 20, no. 5, pp. 1045–1054, Sep. 2005.

- [19] A. H. Weinberg and L. Ghislanzoni, "A new zero voltage and zero current power-switching technique," *IEEE Trans. Power Electron.*, vol. 7, no. 4, pp. 655–665, Oct. 1992.

- [20] W. Qin, X. Wu, and J. Zhang, "A family of dc transformer (DCX) topologies based on new ZVZCS cells with DC resonant capacitance," *IEEE Trans. Power Electron.*, vol. 32, no. 4, pp. 2822–2834, Apr. 2017.

- [21] J. M. Blanes, A. Garrigós, J. A. Carrasco, A. H. Weinberg, and S. Weinberg, "S<sup>3</sup>R optimization for high parasitic capacitance solar arrays," in *Proc. 8th Eur. Space Power Conf.*, 2008.

Carlos Orts was born in Elche, Spain, in 1998. He received the B.Sc. degree in telecommunications technology engineering and the M.Sc. degree in telecommunication engineering from the Miguel Hernández University of Elche (UMH), Elche, Spain, in 2020 and 2022, respectively. He is currently working toward the Ph.D. degree in industrial technologies and telecommunications with the Department of Electronics Technology, UMH.

He is currently a Research Assistant with the Department of Electronics Technology,. His main research interests include space power electronics and their associated systems.

Ausiàs Garrigós (Senior Member, IEEE) was born in Xixona, Spain, in 1976. He received the M.Sc. degree in electronic engineering from the University of Valencia, Valencia, Spain, in 2000, and the Ph.D. degree in space power electronics from the Miguel Hernández University of Elche (UMH), Elche, Spain, in 2007.

He spent research periods with CERN, Switzerland, from 2002 to 2004; the ESA, The Netherlands, in 2008; and the University of Strathclyde, U.K., in 2015. He is currently a

Professor with the Department of Electronics Technology, UMH. He participated in more than 40 research and technology transfer projects and coauthored more than 100 international publications. Most of them related to power electronics. His main research interests include space power electronics and their ancillary electronic systems.

**David Marroquí** was born in Elche, Spain, in 1990. He received the M.Sc. degree in industrial engineering and the Ph.D. degree in industrial technologies from the Miguel Hernández University of Elche (UMH), Elche, in 2015 and 2020, respectively.

He spent a research period with the Center of Reliable Power Electronics, Aalborg University, Denmark, in 2018, as a Predoctoral Researcher, and another period with the European Space Agency, Noordwijk, The Netherlands, during

2021–2022, as a Postdoctoral Researcher. He is currently an Associate Professor with the Department of Materials Science, Optics, and Electronics Technology, UMH. His research interests include space power systems, industrial electronics, and electronics reliability.

Andreas Franke was born in Bavaria, Germany, in 1980. He received the Dipl.-Ing. degree in electrical engineering from the University of Applied Sciences in Kempten, Kempten, Germany, in 2005, and the M.Eng. degree in electrical engineering from the University of Ulster Northern Ireland (UUJ), Coleraine, U.K., in 2006.

He worked in Europe's leading space industry as an Engineer and a Project Manager Team Leader. Since 2012 he has been working with the European Space Agency (ESA), Noordwijk, The

Netherlands, as a High Voltage Power Conditioning Engineer in the Power Management & Distribution Section, Power Systems, EMC & Space Environmental Division, Electrical Department, Directorate of Technology, Engineering & Quality. He is leading many research activities in the field and supporting projects with his expertise, mainly in the domains of electric propulsion, telecom payload, and scientific instruments.